### ORIGINAL RESEARCH PAPER

| Iker Aretxabaleta 🗅 | Iñigo Martínez de Alegría 🗅 |

|---------------------|-----------------------------|

| Unai Ugalde 🗅 🛛     | Iosé Luis Martín 🗈          |

Revised: 5 November 2021

Jose Ignacio Garate 🗅 🗌

Applied Electronic Research Team, University of the Basque Country, Bilbao, Spain

### Correspondence

Unai Ugalde, Applied Electronic Research Team, University of the Basque Country, Bilbao, Spain. Email: unai.ugalde@ehu.eus

Funding information Ministerio de Ciencia e Innovación, Grant/Award Number: MCIN/AEI/10.13039/501100011033 PID2020-115126RB-I0; Eusko Jaurlaritza, Grant/Award Numbers: IT978-16, KK-2020/00077

### Abstract

The shorter switching times of silicon carbide (SiC) MOSFETs enable power converters to operate at higher frequencies than with silicon IGBTs. However, because SiC MOSFET die sizes are still relatively small, several devices have to be connected in parallel to cope with the high current ratings demanded. For the total current to be evenly distributed among all the MOSFETs, the gate circuit and power layout must meet stringent symmetry requirements. However, space limitations on the circuit surface hinders the achievement of full symmetries on both the power and gate layouts because they constrain one another. This paper proposes a solution for safely paralleling discrete SiC MOSFETs while decoupling the gate and power layout designs. It requires placing one BJT-based fast current amplifier as close as possible to each MOSFET rather than using just one to feed all the MOS gates. This reduces the noise in the received gating signals and, more importantly, reduces the sensitivity of driver-gate path geometric / electric mismatches. This makes it possible to safely relax the symmetry requirements for the gating circuitry, thereby providing designers with more freedom to achieve better symmetry in the power layout.

# 1 | INTRODUCTION

The sequence in the evolution of materials used for semiconductor devices anticipated by William Shockley has already reached the level of silicon carbide (SiC) [1–4]. The wellknown trade-off between blocking voltage  $V_{\rm B}$  and specific onresistance  $R_{\rm ON,SP}$  expressed as the figure-of-merit  $V_{\rm B}^2 R_{\rm ON,SP}$  is orders of magnitude higher in SiC than in silicon [5, 6]. However, manufacturers still have to use relatively small die sizes to achieve reasonable product yields [7]. Thus, despite the superior properties of SiC as a base material, in practice SiC MOSFETs must be parallelised to achieve the current levels demanded [8–11].

Given that MOSFETs are unipolar devices, meaning that their  $R_{ON,SP}$  has a positive temperature coefficient that favours an equitable current balance (in contrast to IGBTs'), it is tempting to believe that this implies that they have no specific extra difficulties.

However, this is only true of the drift-region contribution to  $R_{\rm ON,SP}$ , which is dominant once the turn-on transient has died out. Indeed, the channel resistance —whose temperature coefficient is negative— prevails during transients [12]. Moreover, this happens not only in the more mature planar double-diffused structures, but also in younger trench-based gate designs [13].

In addition, it is much harder to grow silica on SiC than on silicon substrates [14]. This poses a substantial challenge for the fabrication of MOS structures and results in, for example, a wider than desirable dispersion of threshold voltages among different devices of the same model [11, 15, 16]. Therefore, effective switching synchronisation is crucial for reliable parallelisation of SiC MOSFETs. Moreover, the switching command must reach all the gates at the same time and rise / fall as simultaneously as possible [17–21].

Active gate driving techniques are a well-known alternative to passive component-based driving circuits [15, 22–24]. Thus, SiC

<sup>7554543, 2022, 4,</sup> Downloaded from https:// nilinelibrary.wiley.com/doi/10.1049/pe12.12232 by Universidad Del Pais Vasco, Wiley Online Library on [17/01/2023]. See the Terms and Conditions (https://onlinelibrary.wiley.com/terms and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons

This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

<sup>© 2022</sup> The Authors. IET Power Electronics published by John Wiley & Sons Ltd on behalf of The Institution of Engineering and Technology

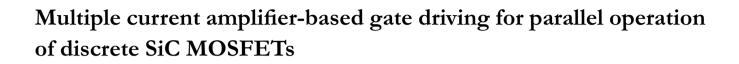

FIGURE 1 A generic push-pull current-amplifying buffer

MOSFET gates are no longer charged through a single resistor, as was usual for their silicon counterparts [7, 10, 25–27]. Most active drives of this type incorporate a push–pull buffer that acts as a current amplifier which speeds up the charging and discharging of MOS capacitance and guarantees faster switching times in spite of the non-negligible stray inductances involved [28, 29].

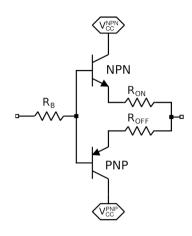

The aim of this paper is to show how to leverage BJTbased current amplification for the parallelisation of discrete (i.e. single-chip) SiC MOSFETs. Thus, this work proposes the use of one buffer per MOSFET instead of a single buffer for all the MOSFETs (compare Figure 2a,b). Each buffer should be placed as close as possible to its corresponding MOSFET. As a result, gate-attack paths carry one gate current each, thereby greatly reducing their effect on stray inductances and improving switching synchronisation.

While this proposal does not erase stray inductances (rather, it passes them back to the driver-buffer paths), it is shown that its overall performance is less sensitive to the mismatch of the driver-buffer path electrical behaviour than it is to that of the buffer-device paths. This can be expected to relax the symmetry requirements on the driving / gating side, thus achieving independence between power-side and driving / gating-side designs. In turn, this would make it easier to optimise the symmetric design of the power side, which is mandatory for good layout practice.

# 2 | EFFECTIVE DRIVER-GATE STRAY INDUCTANCES

Figure 1 depicts a generic BJT-based push-pull buffer. Essentially it comprises an NPN+PNP emitter follower pair so that output current can be sourced as well as sunk. This configuration is widely found in power amplifiers, where it is termed a 'class-B' output stage [30, 31].

When seen from the load side, looking towards the emitter, an emitter follower presents the Thévenin impedance of the source driving its base as though it were  $\beta + 1$  times smaller than it actually is, in addition to a contribution resulting from

FIGURE 2 Typical parallel gating (a) versus new proposal (b)

the emitter dynamic resistance  $r_e$ , sometimes expressed through  $r_{\pi} = (\beta + 1)r_e$ . Therefore, these stages are typically appended to voltage sources that cannot cope with the current levels demanded by their loads.

(b) Large  $L_1 \cdots L_N$  but small  $\ell_1 \approx \cdots \approx \ell_N$ .

Note, however, that the value for  $\beta$  (the current gain of the BJT) should be taken at the frequency of interest, where it is likely to have fallen significantly from its dc-value. This performance degradation, which is usually captured by the BJT's unitgain 'transition frequency' ( $f_T$ ), drops for increasing collector current levels [32].

Figure 2 introduces a MOSFET parallelisation scenario. Because several gates must be fed, a decision has to be made: either use a single buffer to feed all the gates (which cannot possibly be placed near all the gates), or dedicate one buffer to each gate, thus minimising the buffer-gate stray inductance.

Let us compare the s-domain performance of these two setups in terms of  $I_1$ , the current supplied to the first MOS-FET. To simplify these expressions, in this section it is assumed that all the MOSFETs and their gate paths are electrically equivalent, and so  $z_1 = \cdots = z_N$ ,  $L_1 = \cdots = L_N$ , and  $\ell_1 = \cdots =$  $\ell_N \approx \ell_0$ . In addition, both  $R_{\rm ON}$  and  $R_{\rm OFF}$  are set to zero both for simplicity and because no such resistors were used in this work.

• Single-buffer setup. Because the total current provided by the

only stage equals  $NI_1 = \frac{V_0}{\frac{z_0 + s\ell_0 + R_B + r_\pi}{\beta + 1} + \frac{sL_1 + z_1}{N}}$ , then

$$V_1(\text{Single}) = \frac{V_0}{N \frac{z_0 + s\ell_0 + (R_B + r_\pi)}{\beta + 1} + sL_1 + z_1}.$$

(1)

Multiple-buffer setup. Let us imagine that z<sub>0</sub> is split into N equal, parallel-connected impedances of Nz<sub>0</sub> ohms each. Thanks to symmetry, Nz<sub>0</sub> ohms can be assigned to each branch, which means that every branch 'sees' V<sub>0</sub> in series with

$N_{\chi_0}$ , and therefore

$$I_{1}(\text{Multiple}) = \frac{V_{0}}{\frac{N_{z_{0}} + sL_{1} + (R_{B} + r_{\pi})}{\beta + 1} + s\ell_{1} + z_{1}}.$$

(2)

Naturally, the smaller the denominators of (1)-(2), the faster the response and, therefore, the better the performance. These denominators have five addends. Two of them,  $\frac{N_{\tilde{z}_0}}{\beta_{\pm 1}}$  and  $z_1$ , would be kept the same. In addition, the contribution of  $(R_B + r_{\pi})$  would be reduced by a factor of N from (1) to (2).

However, more interestingly, although the effect of the small stray inductance of the edges of the path changes from  $\frac{N\ell_0}{\beta+1}$  to  $\ell_1$ , the bulk of the stray inductance would be reduced by a factor of  $\beta+1$ . This is a major advantage because it reduces the effective Thévenin inductance seen from the gates, and so a faster response can be expected. In addition, because the weight of such inductances in the overall denominator is reduced, the impairment on the synchronisation of the gating signals caused by individual variations of  $L_1 \cdots L_N$  from the average value (resulting from path asymmetries) should also reduce.

Moreover, from the perspective of the dynamic response to a step input, that is, the switching control signal, the behaviour of both setups is equivalent to that of a basic RLC network. Thus, examining the damping factor,  $\alpha = \frac{R}{2L}$ , and the natural frequency,  $\omega_n = \frac{1}{\sqrt{LC}}$ , of both configurations, and bearing in mind that underdamping occurs whenever  $\alpha < \omega_n$ , the inequality  $L > \frac{CR^2}{4}$  applies. As (1) and (2) show, the *C* (within z) and *R* values are approximately the same for both configurations, and the main contribution of the inductance value *L* is due to  $L_1$  and  $\ell_1$ , respectively. Therefore, assuming  $L_1 > \ell_1$ , the single push-pull configuration is more likely to be overdamped than its counterpart in the same conditions, thereby implying that the magnitude and oscillations of *dvdt* in the single-buffer configuration will be higher during switching.

In the following sections these two topologies will be assessed in more detail, also considering possible mismatches in the values of  $L_1 \cdots L_N$ . This means that a total of four cases will be studied: 'single-buffer, symmetric paths' (SS), 'single-buffer, asymmetric paths' (SA), 'multiple-buffer, symmetric paths' (MS), and 'multiple-buffer, asymmetric paths' (MA). However, as it is shown below, the simulated performance of the SA case was so poor and so dangerous that there was little point in considering it for experimental validation.

# 3 | REARRANGING THE CURRENT-AMPLIFYING STAGE

Once the potential interest of the multiple-buffer topology has been justified, according to the methodology followed, it

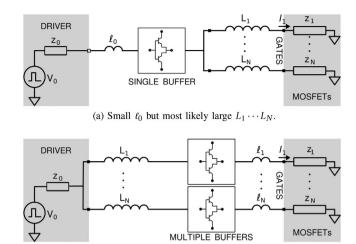

**FIGURE 3** Schematic of the buck converter, emphasising the power part (and ignoring parasitics for clarity)

remains to: (i) select a simple, illustrative power conversion environment; (ii) pre-design the layouts and estimate their bulk stray inductances, (iii) simulate the resulting four circuits, incorporating the models of the active devices involved (including the power switching devices), and finally (iv) develop and implement the relevant cases, to experimentally validate their actual performance.

Thus, one of the simplest converter topologies was chosen (see Figure 3): a standard step-down dc-dc converter running from a 250-V supply, equipped with an output *LC* filter of 200  $\mu$ H and 100  $\mu$ F, and feeding a 20-A d.c. load (although 10 A and 5 A were also considered for some simulations, as it is shown in the following section). As to the power switching, N = 4 SiC MOSFETs (Wolfspeed C3M0075120J) worked in parallel along with four SiC Schottky diodes (STMicroelectronics STPSC20H12G), all switching at f = 125 kHz with a 50% duty cycle.

The current-amplifying buffers (recall Figure 1) were implemented using one PBSS4041NX NPN and one PBSS4041PX PNP, both made by Nexperia. They were selected because of their current handling capabilities and low saturation voltages, in spite of their modest  $f_T$  of 130-110 MHz at ±0.1 A. The collector supply voltages were chosen so that  $V_{CC}^{NPN} = 19$  V and  $V_{CC}^{PNP} = -5$  V. In all the instances,  $R_B$  was set to 47  $\Omega$  in order to maintain the base currents within reasonable ranges. In addition,  $R_{ON} = R_{OFF} = 0$ , and no external gate resistors were added, meaning that  $R_B$  would indirectly limit the speed of the gate charging.

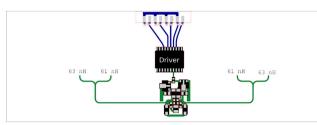

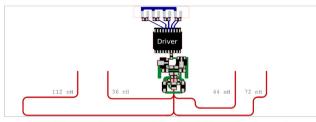

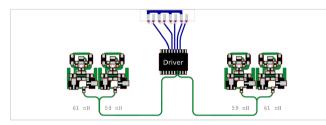

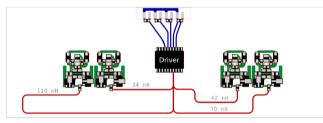

Figures 4 and 5 show the corresponding pre-designed layouts and indicate the estimated bulk stray inductances of the driverto-buffer and buffer-to-gate pathways. Namely, these  $L_1 \cdots L_4$ values were obtained using FastHenry software [33], based on the geometry of the tracks, and switching frequency considerations to account for the skin effect.

For both symmetric layouts, the result of these inductances was nearly identical:  $62\pm1$  nH in the SS case, and  $60\pm1$  nH for the MS case. Subsequently, both topologies were deliberately rerouted wrongly (hence the red-coloured tracks), but because the preliminary simulations gave such a poor (and dangerous) result for the SA case (Figure 6), it was immediately discarded. In contrast, the MA case was based on inductance values of 110, 34, 42, and 70 nH.

(a) SS setup: a single buffer feeds all the gates.

(b) SA setup: the same as above, but deliberately misrouted.

FIGURE 4 Pre-designs of the single-buffer layouts

(a) MS setup: one buffer for each gate.

(b) MA setup: the same as above, but deliberately misrouted.

**FIGURE 6** Extreme turn-on ringing of  $v_{GS}$  in the SA case

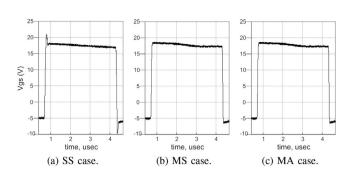

FIGURE 7 Simulated turn-on voltages

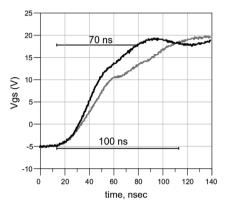

FIGURE 8 Simulated turn-on voltage rising edges: SS (grey) versus MS (black)

# 4 | SOFTWARE SIMULATIONS

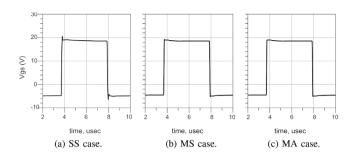

Several simulations were carried out using Keysight's ADS software. They were focused on gaining insight into the shapes of  $v_{GS}(t)$ , the gate-source voltages at the end of the MOSFET, in terms of their overshoots, rise times, and mutual synchronisations. Indeed, the simulations also looked into the waveforms of the drain voltage and drain currents, but no differences could be perceived among the cases studied, and so they provided no useful information in comparative terms.

To begin with, as shown in Figure 6, a significant inductance mismatch would cause the extreme ringing in an SA case and so it was discarded from the following studies.

Figure 7 shows the remaining three cases; in the SS case,  $v_{GS}$  exhibited a noteworthy 2-V overshoot in both the rising and the falling edges. This is in contrast with the well-behaved signal in the MS case. Finally, the signal displayed for the MA case, which corresponds to the branch with the largest driver-to-buffer inductance, was not hindered by this excess stray inductance.

Figure 8 provides a closer look at the rising  $v_{GS}$  edges of the SS and MS cases. In line with the previous observations, the signal of the former rose slower than the latter, that is, 80 versus 55 ns, and so it took a 30% less time for the MS signal to rise.

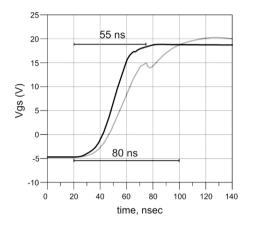

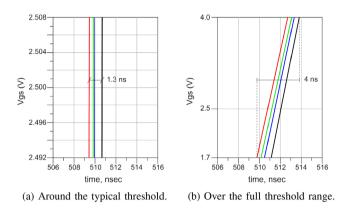

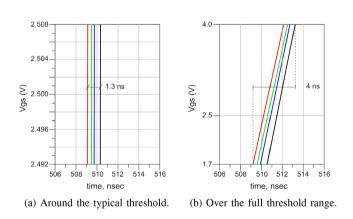

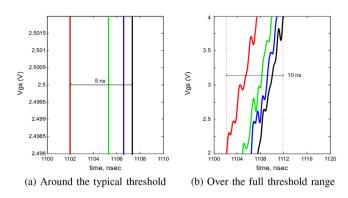

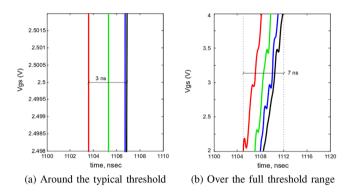

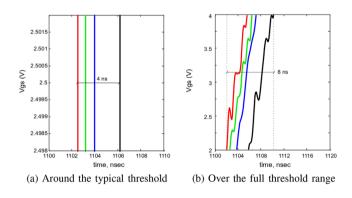

Figure 9 compares the rising edges of the four MA turn-on signals. By zooming in around the typical 2.54-V gate-voltage threshold of the Wolfspeed SiC C3M0075120J MOSFET (see

FIGURE 9 Simulated *v*<sub>GS</sub> rising edges, MA case

FIGURE 10 Rising edges with load current = 10 A

**FIGURE 11** Rising edges with load current = 5 A

Figure 9a), it can be seen that the asymmetry of the inductive paths caused a short 1.3-ns gap between the rising edges of the branches (which had the smallest and largest inductances).

However, over the full range of possible threshold voltages (1.7–4.0 V) the gap increased to 4 ns (see Figure 9b). Nevertheless, because the activation delay of these MOSFETs was about 8 ns, the application of the proposal being presented here seemed to result in an admissible deviation which should not entail critical synchronisation problems. Also note that the same results were obtained with load currents of 10 A and 5 A, as shown in Figures 10 and 11.

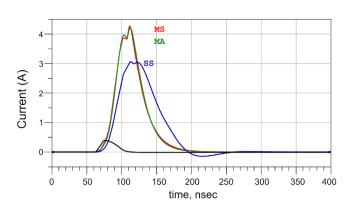

FIGURE 12 Aggregate gate turn-on currents of MS (red), MA (green) and SS (blue) cases; buffer input current also shown (black)

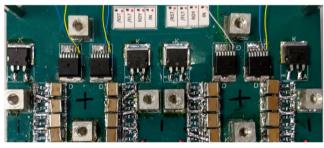

(a) Pre-design of the power layout.

(b) Board with mounted components.

FIGURE 13 Top views of the power area

Finally, it is instructive to briefly analyse the current amplification performance of the buffers. Thus, Figure 12 compares the sum of all four gate currents; the buffer input current (which is the same for both MS and SS) is also shown for reference. Faster rise times are achieved in the multiple buffer cases (MS and MA), and unlike the SS case, there is no negative current at all, leading to more efficient driving of the MOSFETs. This also suggests that the larger the number of parallelised MOSFETs, N, the more noticeable the improvement will be.

# 5 | EXPERIMENTAL VALIDATION AND DISCUSSION

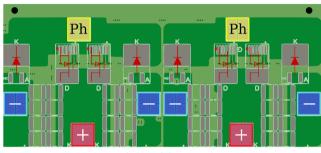

Figure 13 displays the power stage of the buck converter, whose two "Ph" tags correspond to the MOSFET sources and

FIGURE 14 Measured turn-on voltages

FIGURE 15 Measured turn-on voltage rising edges: SS (grey) versus MS (black)

diode cathodes, with two MOSFETs and two diodes joining at each "Ph".

The experimental tests confirmed the benefits that had been anticipated in the simulations. Concerning the turn-on  $v_{GS}$  signals and their overshoots, the measured traces shown in Figure 14 resembled those of Figure 7. The real SS case also clearly overshot (even more markedly at about 3 V) in both its rising and falling edges, whereas the MS and worst-case MA signals both turned out to be neat and well shaped.

In addition, Figure 15 shows the rise times measured for the SS and MS cases. Although they were both longer than those of Figure 8, their relationship is essentially the same: the MS signal rose 30% faster.

Finally, as far as the synchronisation is concerned, the four gate signals had to be measured to account for device parameter dispersion. Figures 16a–18a focus on the typical 2.5-V threshold; the synchronisation between the individual gate voltage signals is exceptionally good in all cases, with the best behaviour exhibited by the MS case with a maximum deviation of 3 ns.

However, when the threshold range is extended to encompass all the values between the minimum and maximum limits provided by the manufacturer, that is, from 1.7 to 4.0 V, the picture completely changes (Figures 16b–18b): 10 ns were measured in the SS case, whereas 7 and 8 ns were measured in the MS and MA cases, respectively.

Thus, given that the activation time of these MOSFETs (provided by their datasheets) lies at around 8 ns, the use of a single buffer could cause serious synchronisation problems, resulting

FIGURE 16 Measured rising edges, SS case

FIGURE 17 Measured rising edges, MS case

FIGURE 18 Measured rising edges, MA case

in one of the MOSFETs being fully on while another is still off. This risk would be greatly reduced if the designer instead opted for the multiple push–pull buffer arrangement, which can also be expected to yield much neater gating signals with 30% shorter turn-on rise times in the cases studied here.

# 6 | CONCLUSIONS

This work deals with the use of BJT-based push-pull buffers as current amplifiers for the gate-attack circuitry of discrete SiC MOSFETs operating in parallel. In particular, it studies the use of one buffer per MOSFET, instead of one single buffer for all MOSFETs, as is usual in commercially available multichip modules. Because the buffers can then be placed very close to their companion MOSFETs, the stray inductance of the driver-to-gate path no longer concentrates on the buffer-togate portion of the path but rather, on the driver-to-buffer portion, through which much lower currents pass.

To assess the benefits of this new setup, one of the simplest possible converter topologies was chosen, namely a step-down dc-dc converter with four MOSFETs in parallel with four fast diodes on the low side. The simulations conducted, as well as their subsequent experimental validation, revealed two important advantages of this setup. On one hand, because the control signals reaching the gates were much neater, harmful overshoots and ringing oscillations were avoided, and therefore the risk of self-turn-on was reduced.

On the other hand, the electric performance was less sensitive to the degree of asymmetry between the diverse buffer-togate paths, which resulted in a reduced risk of non-simultaneous switching. This means that for a given risk, a greater level of asymmetry could be tolerated in the gate-attack circuitry which would, in turn, aid in design efforts to achieve higher symmetry levels on the power-side layout.

### ACKNOWLEDGEMENTS

This work was supported in part by the Government of the Basque Country within the fund for research groups of the Basque University system IT978-16 and by the ELKA-RTEK research program (project ENSOL2-KK-2020/00077) and by the MCIN/AEI/10.13039/501100011033 within the project PID2020-115126RB-I00.

### CONFLICT OF INTEREST

The authors declare no conflict of interest.

## ORCID

IkerAretxabaleta ID https://orcid.org/0000-0001-5651-3786 Iñigo Martínez de Alegría ID https://orcid.org/0000-0001-5203-6169

Jose Ignacio Garate https://orcid.org/0000-0003-0343-6320 Unai Ugalde https://orcid.org/0000-0002-9395-3622 José Luis Martín https://orcid.org/0000-0002-5738-6376

### REFERENCES

- Rahman, M.M., Furukawa, S.: Silicon carbide turns on its power. IEEE Circuits Devices Mag. 8, 22–26 (1992)

- Rabkowski, J., Peftitsis, D., Nee, H.-P.: Silicon carbide power transistors: A new era in power electronics is initiated. IEEE Ind. Electron. Mag. 6, 17–26 (2012)

- Wang, J., Veliadis, V., Zhang, J., Wilson, P.R., Scott, M.J.: IEEE ITRW working group position paper — System integration and application: Silicon carbide. IEEE Power Electron. Mag. 5, 40–44 (2018)

- Liu, G., Li, K., Wang, Y., Luo, H., Luo, H.: Recent advances and trend of HEV/EV-oriented power semiconductors – An overview. IET Power Electron. 13(3), 394–404 (2020)

- Kimoto, T., Cooper, J.A.: Fundamentals of Silicon Carbide Technology. John Wiley & Sons Ltd, Singapore (2014)

- Cooper, J.A., Morisette, D.T.: Performance limits of vertical unipolar power devices in GaN and 4H-SiC. IEEE Electron. Device Lett. 41(6), 892–895 (2020)

- Colmenares, J., Peftitsis, D., Rabkowski, J., Sadik, D.-P., Tolstoy, G., Nee, H.-P.: High-efficiency 312-kVA three-phase interver using parallel connection of silicon carbide MOSFET power modules. IEEE Trans. Ind. Appl. 51(6), 4664–4676 (2015)

- Xiao, Q., Yan, Y., Wu, X., Ren, N., Sheng, K.: A 10kV/200A SiC MOS-FET module with series-parallel hybrid connection of 1200V/50A dies. In: International Symposium on Power Semiconductor Devices and ICs, pp. 349–352. IEEE, Piscataway (2015)

- Fabre, J., Ladoux, P.: Parallel Connection of 1200-V/100-A SiC-MOSFET half-bridge modules. IEEE Trans. Ind. Appl. 52(2), 1669–1676 (2016)

- Peftitsis, D., Rabkowski, J.: Gate and base drivers for silicon carbide power transistors: An overview. IEEE Trans. Power Electron. 31(10), 7194–7213 (2016)

- Bertelshofer, T., März, A., Bakran, M.-M.: Modelling parallel SiC MOS-FETs: Thermal self-stabilisation vs. switching imbalances. IET Power Electron. 12(5), 1071–1078 (2019)

- Li, H., Munk-Nielsen, S., Wang, X., Maheshwari, R., Beczkowski, S., Uhrenfeldt, C., Franke, W.-T.: Influences of device and circuit mismatches on paralleling silicon carbide MOSFETs. IEEE Trans. Power Electron. 31(1), 621–634 (2016)

- Wang, Z., Yang, F., Campbell, S.L., Chinthavali, M.: Characterization of SiC trench MOSFETs in a low-inductance power module package. IEEE Trans. Ind. Appl. 55(4), 4157–4166 (2019)

- Wang, J., Jiang, X.: Review and analysis of SiC MOSFETs' ruggedness and reliability. IET Power Electron. 13(3), 445–455 (2020)

- Xue, Y., Lu, J., Wang, Z., Tolbert, L.M., Blalock, B.J., Wang, F.: Active current balancing for parallel-connected silicon carbide MOSFETs. In: IEEE Transportation Electrification Conference and Expo, pp. 1563– 1569. IEEE, Piscataway (2013)

- Xue, Y., Lu, J., Wang, Z., Tolbert, L.M., Blalock, B.J., Wang, F.: Active compensation of current unbalance in paralleled silicon carbide MOSFETs. In: IEEE Transportation Electrification Conference and Expo. IEEE, Piscataway (2014)

- Wang, G., Mookken, J., Rice, J., Schupbach, M.: Dynamic and static behavior of packaged silicon carbide MOSFETs in paralleled applications. in IEEE Applied Power Electronics Conference and Exposition - APEC, pp. 1478–1483. (2014)

- Guerrero-Guerrero, A.F., Ustariz-Farfan, A.J., Cano-Plata, E.A.: Snubberless balancement in MOSFET stacks by signals gate synchronization with passive components. In: IEEE Workshop on Power Electronics and Power Quality Applications (PEPQA), pp. 1–5. IEEE, Piscataway (2015)

- Horff, R., Bertelshofer, T., Maerz, A., Bakran, M.: Current measurement and gate-resistance mismatch in paralleled phases of high power SiC MOS-FET modules. In: International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management – PCIM Europe, pp. 1–8. IEEE, Piscataway (2016)

- Li, H., Munk-Nielsen, S., Wang, X., Maheshwari, R., Beczkowski, S., Uhrenfeldt, C., Franke, W.: Influences of device and circuit mismatches on paralleling silicon carbide MOSFETs. IEEE Trans. Power Electron. 31(1), 621–634 (2016)

- Raciti, A., Melito, M., Nania, M., Montoro, G.: Effects of the device parameters and circuit mismatches on the static and dynamic behavior of parallel connections of silicon carbide MOSFETs. In: IEEE Energy Conversion Congress and Exposition (ECCE), pp. 1846–1852. IEEE, Piscataway (2018)

- Xue, Y., Wang, Z., Tolbert, L.M., Blalock, B.J.: Analysis and optimization of buffer circuits in high current gate drives. In: IEEE Transportation Electrification Conference and Expo, pp. 1–6. IEEE, Piscataway (2013)

- Anthony, P., McNeill, N., Holliday, D.: High-speed resonant gate driver with controlled peak gate voltage for silicon carbide MOSFETs. IEEE Trans. Ind. Appl. 50(1), 573–583 (2014)

- Shu, L., Zhang, J., Peng, F., Chen, Z.: Active Current Source IGBT Gate Drive with Closed-Loop di/dt and dv/dt Control. IEEE Trans. Power Electron. 32(5), 3787–3796 (2017)

- Rujas, A., López, V.M., Mir, L., Nieva, T.: Gate driver for high power SiC modules: design considerations, development and experimental validation. IET Power Electron. 11(6), 977–983 (2018)

- Anurag, A., Acharya, S., Bhattacharya, S.: Gate drivers for high-frequency application of silicon-carbide MOSFETs. IEEE Power Electron. Mag. 6, 18–31 (2019)

- Sukhatme, Y., Miryala, V.K., Ganesan, P., Hatua, K.: Digitally controlled gate current source-based active gate driver for silicon carbide MOSFETs. IEEE Trans. Ind. Electron. 67(12), 10121–10133 (2020)

- Cui, T., Ma, Q., Xu, P., Wang, Y.: Analysis and optimization of power MOS-FETs shaped switching transients for reduced EMI generation. IEEE Access 5, 20440–20448 (2017)

- Miryala, V.K., Hatua, K.: Low-cost analogue active gate driver for SiC MOSFET to enable operation in higher parasitic environment. IET Power Electron. 13(3), 463–474 (2020)

- Horowitz, P., Hill, W.: The Art of Electronics, 3rd ed. Cambridge University Press, Cambridge (2015)

- Sedra, A.S., Smith, K.C.: Microelectronic Circuits, international 7th ed. Oxford University Press, Oxford (2016)

- 32. Horowitz, P., Hill, W.: The Art of Electronics: The x-Chapters. Cambridge University Press, Cambridge (2020)

- Kamon, M., Tsuk, M.J., White, J.: Fasthenry: A multipole-accelerated 3-D inductance extraction program. In: 30th ACM/IEEE Design Automation Conference, pp. 678–683. IEEE, Piscataway (1993)

How to cite this article: Aretxabaleta, I., Martínez de Alegría, I., Garate, J.I., Ugalde, U., Martín, J.L.: Multiple current amplifier-based gate driving for parallel operation of discrete SiC MOSFETs. IET Power Electron. 15, 317–324 (2022). https://doi.org/10.1049/pel2.12232