### CRANFIELD UNIVERSITY

# OSCAR ZAYAS QUINTANA

# HIGH QUALITY FRAME GRABBER FOR AN IR IMAGING CAMERA

# SCHOOL OF AEROSPACE, TRANSPORT AND MANUFACTURING

Computational and Software Techniques in Engineering MSc: Digital Signal and Image Processing

MASTER OF SCIENCE Academic Year: 2015 - 2016

Supervisor: Dr Jane Hodgkinson August 2016

#### CRANFIELD UNIVERSITY

# SCHOOL OF AEROSPACE, TRANSPORT AND MANUFACTURING

Computational and Software Techniques in Engineering MSc: Digital Signal and Image Processing

MASTER OF SCIENCE

Academic Year 2015 - 2016

OSCAR ZAYAS QUINTANA

High quality frame grabber for a IR imaging camera

Supervisor: Jane Hodgkinson August 2016

This thesis is submitted in partial fulfilment of the requirements for the degree of Master of Science

© Cranfield University 2016. All rights reserved. No part of this publication may be reproduced without the written permission of the copyright owner.

# **ABSTRACT**

Image processing techniques represent an ever-growing field of engineering, which is nowadays taking a great importance in a number of sectors as diverse as gas sensing or three-dimensional imaging. In order to satisfy the high demand of imaging systems, not only new cameras are needed, but also a great deal of frame grabbers in charge of collecting and processing the data captured by those cameras. These frame grabbers must be customised for each camera, dealing with its specific features and operation protocols.

In this MSc thesis, a new frame grabber was designed and developed, customised for an innovative infrared imaging camera. The system is based in a FPGA device, making use of an external ADC converter to digitalise the video data coming from the camera and a 2 MB SRAM memory to save this data. The whole development is done by means of VHDL language, a low level hardware description language (HDL) used for FPGA design.

The result of the project is a fully operating frame grabber, with a number of parameters configurable by the final user and with two operation modes for the final user plus one for calibrating the system. The ones for the final user are: one for the creation of a real time video stream (up to 12 fps) and the other one for buffering up to 254 images at high speed (capture rate up to 1025 fps). Besides, only 2% of the logic resources of the FPGA were used.

Thus, a high quality and inexpensive infrared imaging system was developed. Furthermore, the universal nature of VHDL design and the reduced number of resources employed make the migration to a simpler and cheaper FPGA an easy task. On the other hand, the RS-232 standard used for the transmission of data to the final computer is the only bottleneck of the system, and it could be substituted with a faster standard without modifying any other part of the design.

#### Keywords:

FPGA, infrared camera, InGaAs sensor, image processing, VHDL, Hamamatsu, Altera, Gas Sensing, image processing.

### **ACKNOWLEDGEMENTS**

I would like to express my greatest gratitude to Dr Jane Hodgkinson, my supervisor, for her wise advice every time I asked for it, always patient and willing to assist me. Besides my supervisor, I could not be more grateful to Dr Thomas Kissinger and Dr Tom Charret, who were deeply involved in the project since the very beginning, providing me with technical support every time I needed it. The success of this thesis would have not been possible without any of them.

I am also immensely thankful to my family for their moral encouragement and infinite patience during the last times. I will always be in debt to you.

Last but not least, I would like to show my appreciation to all those who, directly or indirectly, lent a hand in the development of this thesis.

# **TABLE OF CONTENTS**

| ABSTRACT                                                      | i    |

|---------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                              | ii   |

| LIST OF FIGURES                                               | v    |

| LIST OF TABLES                                                | viii |

| LIST OF EQUATIONS                                             |      |

| LIST OF ABBREVIATIONS                                         | x    |

| 1 INTRODUCTION                                                | 1    |

| 1.1 Context                                                   | 1    |

| 1.2 Structure of this report                                  | 2    |

| 2 LITERATURE REVIEW                                           | 4    |

| 2.1 Introduction                                              | 4    |

| 2.2 Applications                                              | 5    |

| 2.2.1 Gas Sensing                                             | 5    |

| 2.2.2 Manufacturing                                           | 8    |

| 2.2.3 Medical Imaging:                                        | 8    |

| 2.2.4 Stereo Vision                                           | _    |

| 2.3 FPGA based frame grabbers                                 |      |

| 2.3.1 Related work                                            |      |

| 2.3.2 Alternatives                                            |      |

| 2.4 Communication standards for image transmission            |      |

| 2.4.1 SDI (Serial Digital Interface):                         |      |

| 2.4.2 HDMI (High Definition Multimedia Interface):            |      |

| 2.4.3 USB (Universal Serial Bus):                             |      |

| 2.4.4 GigE (Gigabit Ethernet):                                |      |

| 2.4.5 PCI Express (Peripheral Component Interconnect Express) |      |

| 2.4.6 RS-232:                                                 |      |

| 2.4.7 RS-422                                                  |      |

| 2.5 Summary                                                   |      |

| 3 DESIGNED SYSTEM                                             |      |

| 3.1 Preliminary decisions                                     |      |

| 3.2 General Description of the system and Equipment           |      |

| 3.2.1 The Hamamatsu Image Sensor (G11097-0606S)               |      |

| 3.2.2 The frame grabber                                       |      |

| 3.2.3 Computer                                                |      |

| 3.2.4 Other hardware                                          |      |

| 3.3 Architecture of the IR imaging system                     |      |

| 4 DEVELOPMENT OF THE SYSTEM                                   |      |

| 4.1 Building Blocks                                           |      |

| 4.1.1 SRAM read/write module.                                 |      |

| 4.1.2 UART modules                                            | 37   |

| 4.1.3 Mirror test for the Data Acquisition Card (ADC and HSMC | connection 2 |

|---------------------------------------------------------------|--------------|

| test)                                                         | 38           |

| 4.1.4 Hamamatsu Debug Module                                  | 38           |

| 4.2 Basic version                                             | 40           |

| 4.2.1 Integration Time                                        | 41           |

| 4.2.2 Collecting the image's data in the frame grabber        | 41           |

| 4.2.3 Transmitting the image's data                           | 43           |

| 4.3 Live and Buffer modes                                     | 45           |

| 4.3.1 Parameters configuration                                | 46           |

| 4.3.2 Live mode                                               | 50           |

| 4.3.3 Buffer Mode                                             | 53           |

| 4.4 Adapting the design to the real camera                    | 56           |

| 4.4.1 Creating the clean AD_TRIG signal                       |              |

| 4.4.2 Creating the Calibration Mode                           | 61           |

| 4.4.3 Calculating the real value of the pixel                 | 64           |

| 5 RESULTS                                                     | 66           |

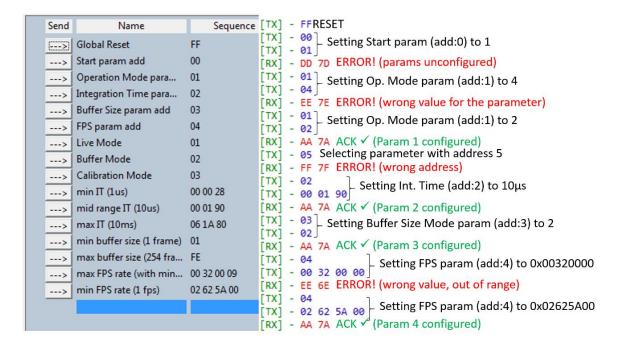

| 5.1 Parameters configuration protocol                         |              |

| 5.2 Received raw data                                         | 66           |

| 5.3 Received images (decoded raw data)                        | 69           |

| 5.4 Performance                                               | 76           |

| 6 CONCLUSIONS AND FUTURE WORK                                 |              |

| REFERENCES                                                    | 80           |

| APPENDICES                                                    | 85           |

# **LIST OF FIGURES**

| Figure 2-1. Outdoor methane leak [3] detected with a gas imaging system [image taken from [6]]6                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-2. Image of sample gas bags (top left), low-resolution gas data (bottom left), gas data interpolated (bottom right) and combined images (top right) [7]. (image taken from [7]) |

| Figure 2-3. IR image (B) vs traditional X-ray image of a lesion in a tooth (image taken from [10])9                                                                                      |

| Figure 2-4. Three-dimensional estimation of a surface using stereo vision techniques (image taken from [14])10                                                                           |

| Figure 2-5. BNC connector and NRZI codification example (image taken from [20])                                                                                                          |

| Figure 2-6. HDMI connectors (image taken from [22])                                                                                                                                      |

| Figure 2-7. USB connector (image taken from [23])                                                                                                                                        |

| Figure 2-8. Connectors and sockets of 1000Base-X (left, optical fibre) and 1000Base-T (right, UTP) (image taken from [26])                                                               |

| Figure 2-9. PCI Express x16 (top, 164 pins) and PCI Express x1 (bottom, 36 pins) connectors (image taken from [29])                                                                      |

| Figure 2-10. DB9 female (left) and male (right) for RS-232 communications (image taken from [32])                                                                                        |

| Figure 3-1. Overview of the IR imaging system26                                                                                                                                          |

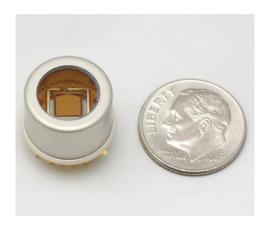

| Figure 3-2. Hamamatsu sensor (image from [36])27                                                                                                                                         |

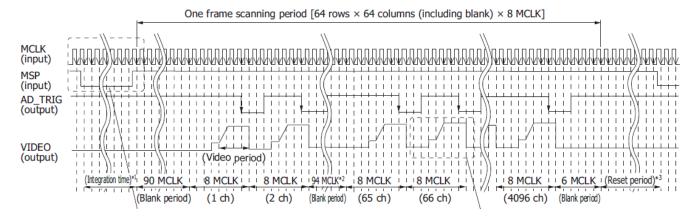

| Figure 3-3. Timing diagram of the camera's signals (image taken from [36]) 28                                                                                                            |

| Figure 3-4. Altera DE2-115 Evaluation Board (image taken from [37]) 30                                                                                                                   |

| Figure 3-5. AD/DA Data Conversion Card (image taken from [38]) 30                                                                                                                        |

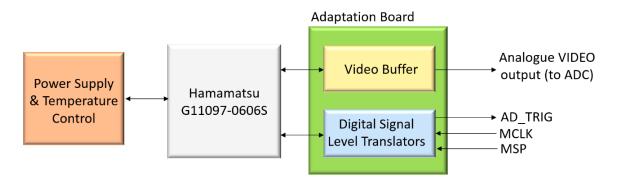

| Figure 3-6. Blocks diagram of the adaptation of Hamamatsu imaging sensor to the overall system                                                                                           |

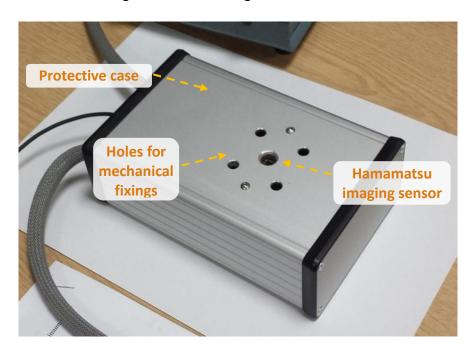

| Figure 3-7. Protective case containing the IR camera chip and the adaptation board                                                                                                       |

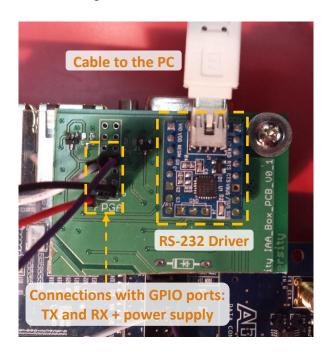

| Figure 3-8. External platform affixed in a corner of the Evaluation Board 33                                                                                                             |

| Figure 3-9. Architecture of the IR imaging system                                                                                                                                        |

| Figure 3-10. Connections in the Data Acquisition Card                                                                                                                                    |

| Figure 3-11. GPIO ports connections                                                                                                                                                      |

| Figure 4-1. Pinout of the Hamamatsu Debug Module                                                                        |

|-------------------------------------------------------------------------------------------------------------------------|

| Figure 4-2. Simulation of the Hamamatsu Debug Module                                                                    |

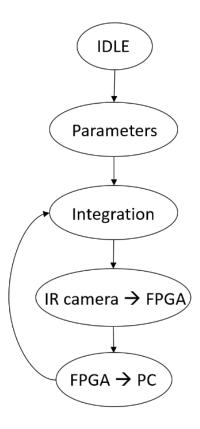

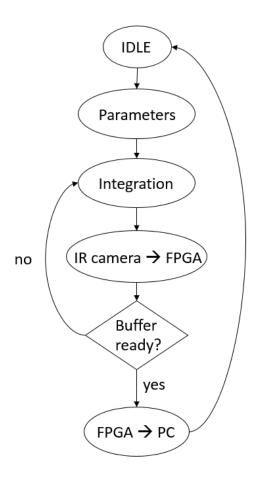

| Figure 4-3. Flow diagram of the basic version of the system 41                                                          |

| Figure 4-4. Beginning of the communication between the camera and the frame grabber                                     |

| Figure 4-5. Saving the last pixel of the image in its corresponding position (4095 <sup>th</sup> ) in the SRAM memory   |

| Figure 4-6. Transmission of the first pixel of the image (first byte) 44                                                |

| Figure 4-7. Transmission of the second pixel of the image (second byte) 45                                              |

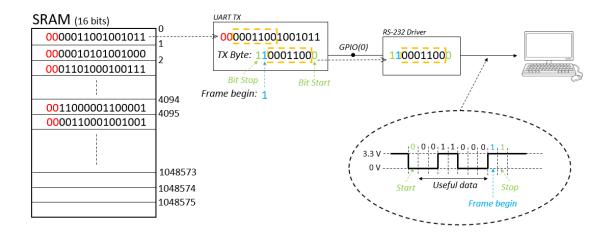

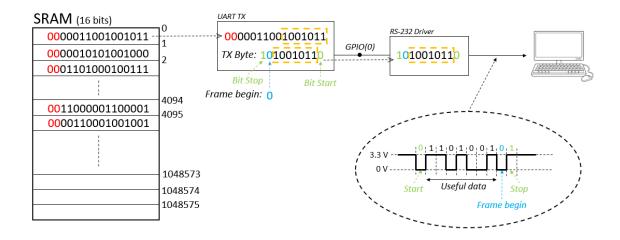

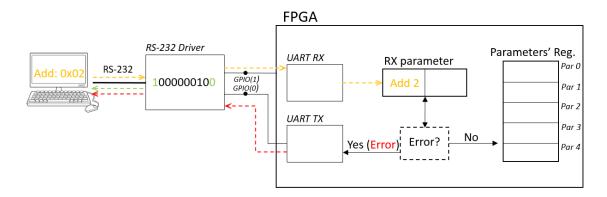

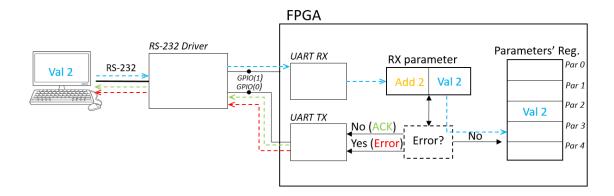

| Figure 4-8. Configuring the parameter with address 0x02 (1) 47                                                          |

| Figure 4-9. Configuring the parameter with address 0x02 (2)                                                             |

| Figure 4-10. Flow diagram of the Live Mode51                                                                            |

| Figure 4-11. Flow diagram of the Buffer Mode53                                                                          |

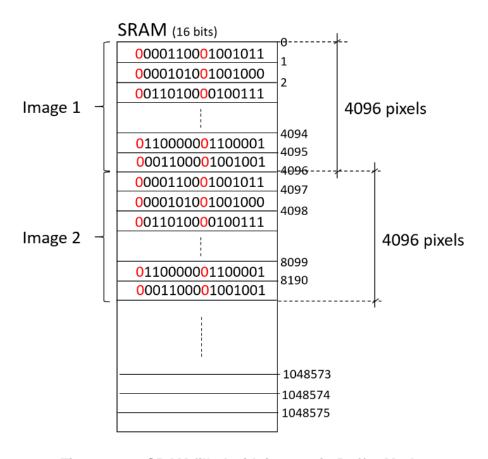

| Figure 4-12. SRAM filled with images in Buffer Mode                                                                     |

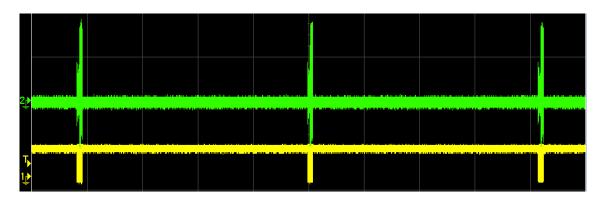

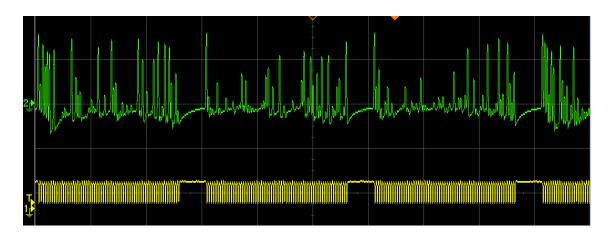

| Figure 4-13 VIDEO (green) and AD_TRIG (yellow) signals with the frame grabber running in Live Mode (1)                  |

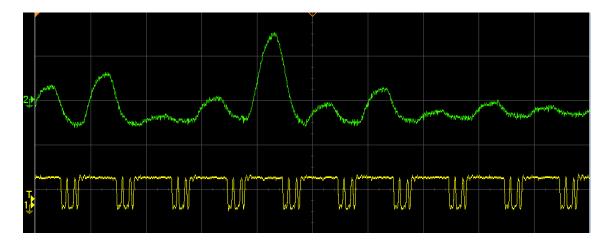

| Figure 4-14. VIDEO (green) and AD_TRIG (yellow) signals with the frame grabber running in Live Mode (2)                 |

| Figure 4-15. VIDEO (green) and AD_TRIG (yellow) signals with the frame grabber running in Live Mode (3)                 |

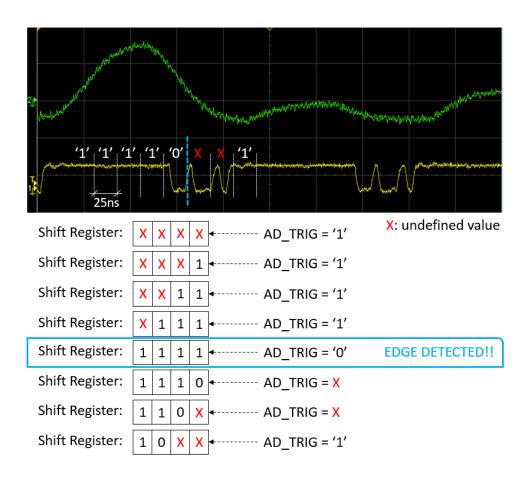

| Figure 4-16. Process of detecting falling edges in the original AD_TRIG 60                                              |

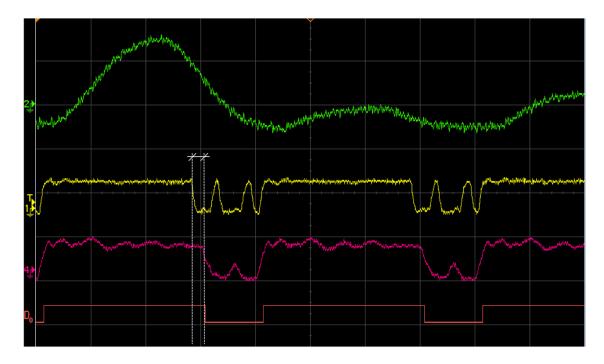

| Figure 4-17. VIDEO (green), original AD_TRIG (yellow), and clean AD_TRIG read as both analogue (pink) and digital (red) |

| Figure 4-18. Digitalised values of the VIDEO signal around the first falling edge of the clean AD_TRIG signal           |

| Figure 5-1. Example of configuration sequence                                                                           |

| Figure 5-2. Example of image reception from the Hamamatsu Debug Module (first image of the stream)                      |

| Figure 5-3. Example of image reception from the Hamamatsu Debug Module (any image in the stream after the first one)    |

| Figure 5-4. Example of image reception from the real IR camera (first image of the stream)                              |

| Figure 5-5. Example of image reception from the real camera (any image in the stream after the first one)               |

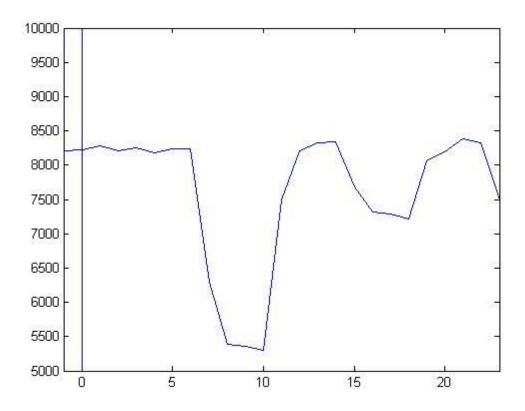

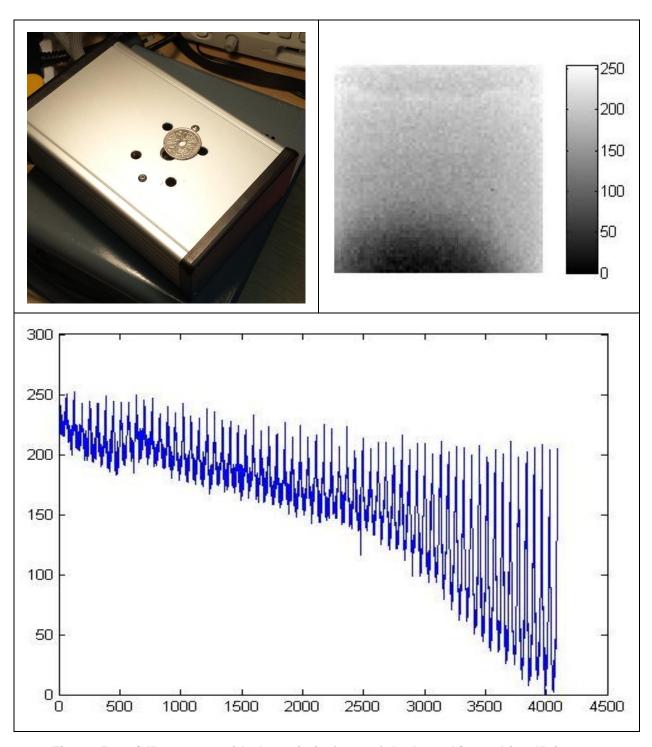

| Figure 5-6. a) IR camera with the coin in front of the lens; b) resulting IR image; c) resulting signal plotted70                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-7. 10 buffered images received in a row71                                                                                                 |

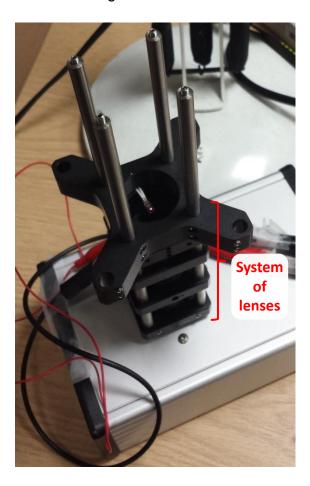

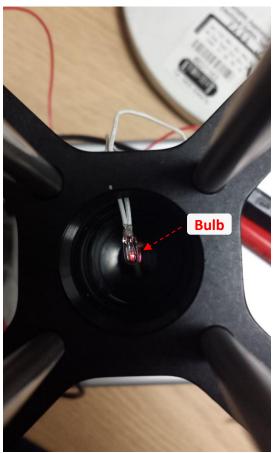

| Figure 5-8. System of lenses for focusing the bulb72                                                                                               |

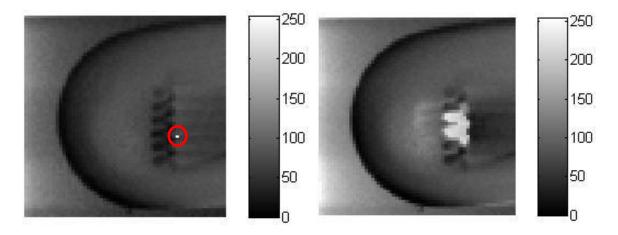

| Figure 5-9. Images of the bulb off (left) and on (right)73                                                                                         |

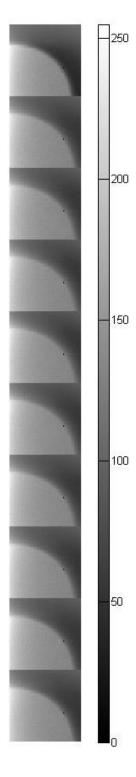

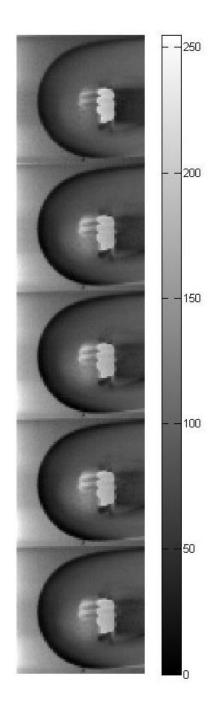

| Figure 5-10. 5 frames transition of the bulb, captured in buffer mode at 1015 fps                                                                  |

| Figure 5-11. 5 frames transition of the bulb, captured in buffer mode at 1015 fps (signal plotted)75                                               |

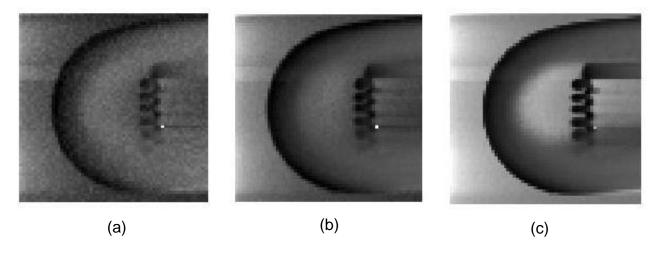

| Figure 5-12. Images captured varying only the exposure time: a) 2.925µs, b) 6.4µs, c) 10µs                                                         |

| Figure A-1. Simplified (left) and complete (right) flow diagrams of the basic version                                                              |

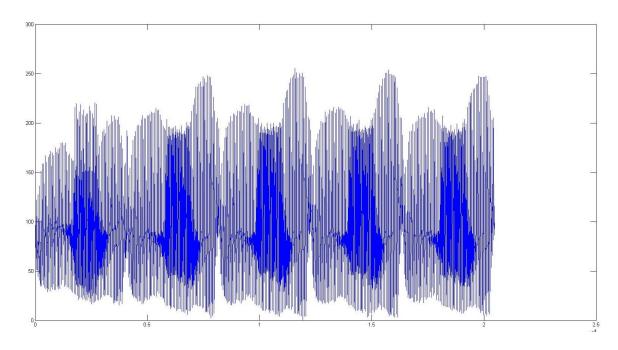

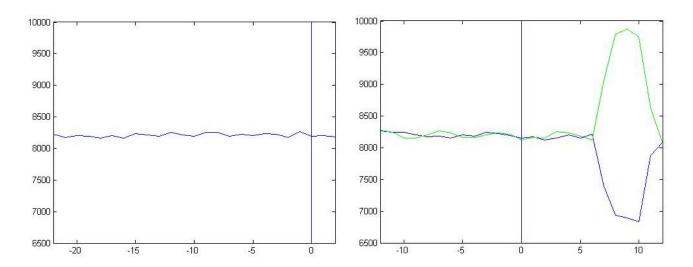

| Figure B-1. VIDEO signal plotted with data of Calibration Mode, with the window shifted to the left of the trigger (left) and to the right (right) |

# **LIST OF TABLES**

| Table 2-1. SDI standards                                                                    |

|---------------------------------------------------------------------------------------------|

| Table 2-2. HDMI versions                                                                    |

| Table 2-3. USB versions                                                                     |

| Table 2-4. Versions and data rates of PCI Express                                           |

| Table 2-5. Summary of data rates of the main communication standards used in frame grabbers |

| Table 4-1. Parameters' addresses and allowed values                                         |

| Table 4-2. Error and acknowledgement codes                                                  |

| Table 4-3. Timings in Live Mode                                                             |

| Table 4-4. Maximum throughputs in Live Mode                                                 |

| Table 4-5. Reference image capture rates in Buffer Mode 55                                  |

| Table 4-6. Operation Mode parameter's addresses and allowed values 62                       |

| Table 5-1. FPGA usage percentage values77                                                   |

# **LIST OF EQUATIONS**

| (4-1) | ) | 49 |

|-------|---|----|

| (4-2) | ) | 55 |

# LIST OF ABBREVIATIONS

ADC Analogue to Digital Converter

CLK Clock

FPGA Field Programmable Gate Array

FPS Frames Per Second

GPIO General-Purpose Input/Output

GUI Graphical User Interface

HDL Hardware Description Language

HDMI High Definition Multimedia Interface

IEEE Institute of Electrical and Electronics Engineers

IR Infrared

LAN Local Area Network

LSB Least Significant Bit

MCLK Master Clock

MSB Most Significant Bit

MSP Master Start Pulse

ROM Read-Only Memory

SRAM Static Random-Access Memory

TTL Transistor-Transistor Logic

UART Universal Asynchronous Receiver/Transmitter

UART RX UART Reception

UART TX UART Transmission

UTP Unshielded Twisted Pair

USB Universal Serial Bus

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

## 1 INTRODUCTION

#### 1.1 Context

After a long time under development, image processing is no longer a field of conceptual experimentation, but a reality in terms of practical implementation. Nowadays, these techniques mean both the implementation of innovative methods and the substitution of traditional methods with more efficient and autonomous alternatives, being used in a number of different sectors: gas sensing, medical industry, stereo vision...

In the case of gas sensing, capturing images within the infrared wavelengths range, different gas leakages can be detected. Due to the typically low resolution of some infrared imaging cameras, certain image processing techniques must be applied for each specific system, such as the interpolation of low resolution images in order to obtain the shape of a real gas cloud. Another example of image processing is the technique used for creating stereo vision, where the images coming from two cameras placed one next to the other and focusing to the same point are compared, obtaining a disparity image that provides an output with a three-dimensional effect.

There is a wide variety of cameras available in the market, each of them with different features (infrared imaging, high resolution...) depending on the target application, but all have something in common: the need of a frame grabber for collecting the captured images and transmitting them to a computer. Apart from this, the frame grabbers can also perform the specific image processing techniques requested for each application. However, the process of collecting and transmitting the data is not a trivial task and, being this the basis for any frame grabber, it is paramount to design and develop this part of the system as accurately as possible.

Regarding the technology used for building the frame grabbers, there are some compelling reasons why traditional systems are all based in FPGAs, which are devices composed of a large matrix of logic gates configurable by means of HDL languages. This devices allow the designer to split the processing

algorithms in different parts and to implement them in parallel, working with high frequency clocks. These features make possible to dramatically decrease the latency between video frames. Besides, being HDL low level languages, they are intended to work at bit level and to control the state of every signal in every clock period, which is essential to synchronise the electronic system with any camera.

The motivation for this thesis came with the release of a cheap 64x64 InGaAs image sensor for infrared imaging by Hamamatsu. Traditionally, a sensor with these features could cost tens of thousands of pounds, whilst the one by Hamamatsu is available for £1500. In respect to the type of sensor, the ones based in InGaAs photodiodes cover the wavelength range from ~800 nm to 1700nm, within which many gases absorb the light, whereas standard silicon cameras stop at 1000 nm. Therefore, this kind of sensors are extremely useful for gas sensing applications. On the other hand, the Group of Engineering Photonics of Cranfield University has a research line in gas sensing, where the use of IR cameras is essential, and they had acquired the IR imaging sensor created by Hamamatsu. In this context, the need of a frame grabber able to collect the images captured by the InGaAs image sensor was clear, since it would allow the use of this innovative sensor in future researches.

# 1.2 Structure of this report

This report is arranged in 5 main sections. In the INTRODUCTION, the project is put into context and the motivation for its development is stated.

In Section 2 (LITERATURE REVIEW) a brief synopsis of the preliminary research is provided. In this section, a deeper view into the frame grabbers is given, explaining some important applications for this systems and their general architecture in the work previously done in the field. Besides, the most suitable communication standards for the transmission of the images are presented.

In Section 3 (DESIGNED SYSTEM) section, an overview of the system is given, presenting the equipment used for the development and giving a detailed view of the system's architecture.

In section 4 (DEVELOPMENT OF THE SYSTEM) all the details of the development process are stated, outlining the challenges and problems faced during the process and explaining the approach taken to overcome them. This section is separated in four subsections, each of them dedicated to a stage of the development.

In Section 5 (RESULTS) the results obtained with the developed imaging system are presented in different forms. First, the raw data received in the computer is shown and explained. Secondly, the useful data signal decoded from the raw data is presented, along with the data in image format. Besides, the performance of the frame grabber in terms of transmission and capture time is stated, and the usage of the FPGA device's resources is also shown.

In Section 6 (CONCLUSIONS AND FUTURE WORK), the conclusions for the results obtained in the previous section are explained, and future work that could be done to improve the system is stated.

## **2 LITERATURE REVIEW**

#### 2.1 Introduction

A frame grabber is an electronic device aimed to capture, store and transmit frames from an analogue video signal or digital video stream, being also useful for performing image processing in certain applications. Initially, frame grabbers were able to store only one frame of video, but modern ones are already able to store multiple frames, allowing even the capture of multiple video streams concurrently.

Regarding the image processing capabilities, there are many techniques usually performed in frame grabbers, which could well be classified in the following main categories[1]:

- Transformation of an image into a new image of the same class. E.g. linear and nonlinear filtering, image resizing.

- Combination of two (or more) different images for the creation of a single output image of the same type, by means of combining every pair of elements from the input images.

- Measurement of an image in terms of descriptive statistics, reducing the input image into a scalar or vector containing information such as mean or standard deviation of pixel values.

- Conversion of an image into an image of a different class. E.g. Discrete Fourier Transform.

Among all the available image processing operations, the image resizing and real time compression (using algorithms like MPEG) [2] stand out due to their potential towards decreasing the delay between frames.

However, any image processing technique performed in a frame grabber relies heavily on the plain process of collecting the data coming from the source of video, converting it into useful digital formats and transmitting it to the opposite endpoint. The development of a system able to perform this process in a reliable way is not a trivial task, and it is clearly the most important part in the

development of any frame grabber with further capabilities. Therefore, the development of this basis is the main target for this project.

# 2.2 Applications

There are several applications in which the fast rates and resolution of frame grabbers are paramount, having led the technology to great developments in those aspects. Some of the most remarkable applications are found within the next categories:

- Gas Sensing

- Manufacturing

- Medical Imaging

- Stereo Vision

- Consumer Devices

- Surveillance Cameras

The most relevant of these categories in terms of scientific and technological innovation are now explained in more detail.

#### 2.2.1 Gas Sensing

Aimed to detect and measure gas concentrations in different environments, the field of Gas Sensing brings one important application for the targeted frame grabber, since the final imaging system will be mainly used for this purpose. The application of gas sensing is highly valuable for a wide range of applications, from safety in process and petrochemical industries to the monitoring of different gas species (e.g. greenhouse gases) in atmospheric science[3][4].

Gas sensing is a difficult task, with traditional systems limited to detect leaks a short distance away due to the nature of the point sampling detectors in which they are based. Besides, it is hard to set the "zero trace" for which there is no leakage in every single point [5].

On the other hand, traditional systems are not only inefficient in terms of technical implementation, but also in the economic aspect, since sensors are supposed to be installed every 5-6m. Therefore, the deployment of a traditional system also involves a great cost.

In this context, imaging gas leaks brings the great advantage of covering wide areas from a remote position with an only IR camera. Furthermore, the leakage source could be directly found, along with the wind direction, and multisource-leakages could be more easily identified [5].

Based in the optical absorption of the gas species [3], any imaging system developed for this application requires the selected camera to capture images in the IR range, since gases absorb light within this range and can only be visualised with a sensor able to detect this frequencies, which is not achieved with conventional cameras. This is the reason why this project will be based on an IR camera.

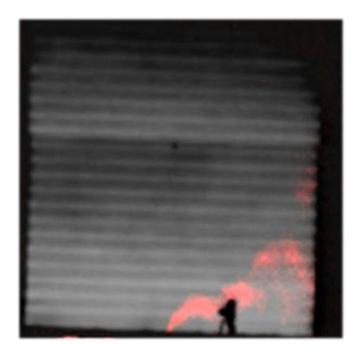

Figure 2-1 shows an image of a gas leakage detected with a gas imaging system:

Figure 2-1. Outdoor methane leak [3] detected with a gas imaging system [image taken from [6]]

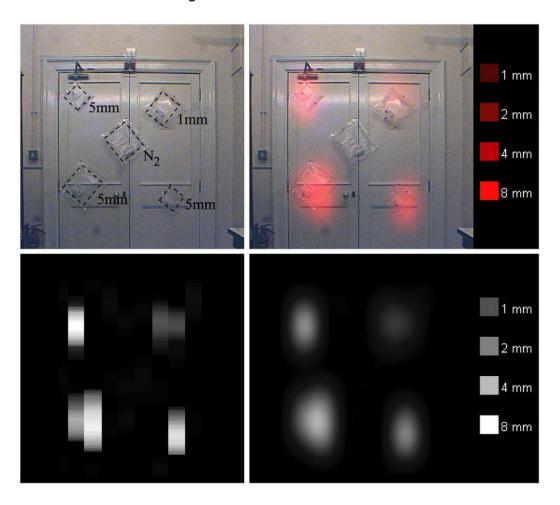

On the other hand, regarding the dimensions of the IR images needed for this application, Graham Gibson et. al. [7] proved that image dimensions as reduced as 10x10 pixels are enough for the effective detection of gas leakages. Making use of an incident laser, they combined the resulting beams scanned over an area (single points) to create low-resolution images (10x10 pixels). Later, these low resolution images are interpolated in order to create the image of a gas cloud detected in a highly reliable way, which is combined with a high resolution image of the scene [7]. Thus, 10x10 images created from individually scanned points can be enough to locate gas emissions in a certain scene. The process and results are shown in Figure 2-2:

Figure 2-2. Image of sample gas bags (top left), low-resolution gas data (bottom left), gas data interpolated (bottom right) and combined images (top right) [7].

(image taken from [7])

#### 2.2.2 Manufacturing

The most representative example of industrial applications is the use of frame grabbers in pick and place machines, implementing vision guidance systems. With the use of this robots for production's automation, the productivity and accuracy are hugely improved, whilst decreasing the costs [8]. Those machines are monitored with cameras whose images are collected and processed with frame grabbers that convert the data to a format understandable for the machines.

During the last ages, major improvements have been made in this field, such as 3D image calibrations, which means estimating the parameters for the interaction among the machine, the camera and the objects' coordinates, allowing the calculation of robot's trajectory using the collected 3D data [8]. In this process, frame grabbers play a crucial role.

#### 2.2.3 Medical Imaging:

In modern operating room environments, highly accurate and low-latency video images are needed for surgery procedures (i.e. X-ray, ultrasound and endoscopy). Since the data can be received in different formats from diverse sources, a quick and reliable normalization is essential [9]. This task is usually performed by high resolution frame grabbers, providing resolutions of up to 1080p in space, 60 fps in time and 10 bit in terms of pixel definition [9].

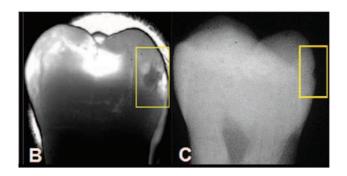

Besides, IR cameras can be particularly interesting in the field of medical imaging due to their high sensitivity to temperatures, and because some materials present a high absorption at certain IR wavelengths. The applications or IR medical imaging are as diverse as the early detection of dental decay thanks to the low light scattering of dental enamel at certain IR wavelengths [10] (see Figure 2-3), or the diagnosis of body diseased parts by means of temperature anomalies [11], being able to detect even breast tumours [12].

Figure 2-3. IR image (B) vs traditional X-ray image of a lesion in a tooth (image taken from [10])

#### 2.2.4 Stereo Vision

Most commonly known as three-dimensional imaging, stereo vision has been a burgeoning field during the last years. Based in two video input streams generated with two cameras that recreate the position of the human eyes, pointing to the same objective and placed with a slight separation between them, the use of frame grabbers for developing the image processing modules necessary to create the disparity image is particularly useful. The disparity image shows the difference in terms of the image location of an object pointed with both cameras of the stereo vision system.

Thanks to the performance of the FPGAs, the stereo vision processing HW implementation (in FPGA) can be hundreds of times faster than the processing performed in conventional computers [13].

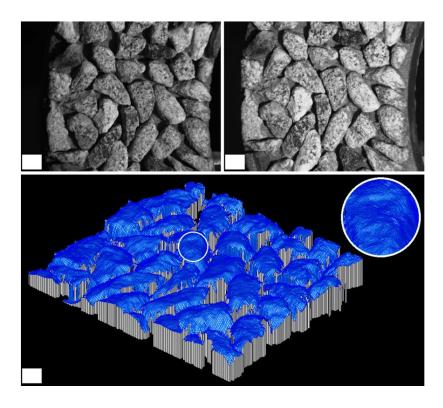

An example of three-dimensional estimation of a surface is shown in Figure 2-4:

Figure 2-4. Three-dimensional estimation of a surface using stereo vision techniques (image taken from [14])

# 2.3 FPGA based frame grabbers

Field Programmable Gate Array (FPGA) chips are integrated circuits aimed to be configured after the production process. The internal logic of the chip can be fitted to the particular needs of each application, providing the final user with a great flexibility. The internal logic is composed of an array of gates that can be interconnected however the designer wants to perform complex logical operations. Those relationships can be easily defined by means of Hardware Description Languages (HDL), such as VHDL or Verilog.

Thus, the user can easily design complex electronic systems that, afterwards, can be either transferred to hard-wired designs for manufacturing targeted to end users, or be used simply integrating the FPGA in a more complex system, facilitating the alteration of the electronics when updates or corrections are needed.

When designing a frame grabber system, the use of an FPGA as a base for it is a really valuable choice. There are multiple reasons for this, but the main ones are related to the performance of the device, making FPGA-based frame grabbers particularly useful for applications that require low latency between processed frames, being the latency the time that the data of a certain frame needs to traverse all the system.

FPGAs allow the parallel implementation of different processes. Thus, a vision algorithm can be split into multiple iterative processes that can be performed in parallel on the FPGA. In fact, many image processing algorithms operate in parallel, what makes them suitable for running on FPGA based frame grabbers [15].

Furthermore, FPGAs are able to receive images data and process individual bits at rates as high as hundreds of MHz (depending on the particular clock), performing the data transfer and processing in every clock cycle and achieving a high-speed bit-level processing [15]. For this two reasons, the image processing time is reduced and therefore the latency between frames is decreased significantly.

Another important reason for choosing FPGA devices is that, being configured by means of low level languages (HDL languages), they are prepared for working at bit level, offering a full control of every bit involved in the operation in each clock cycle. This feature is essential for the development of a frame grabber, because the communication between the system and the camera must be adapted to the specific protocol of the camera in order to collect the images correctly.

Apart from this, there are other great assets that could be really valuable in the FPGA-based frame grabbers, such as the flexibility and accuracy provided by a system whose functionality could be altered by means of a simple modification in the HDL code, or the reduced sized of the whole system thanks to the small package of any FPGA. Besides, for applications in which power consumption is a serious constraint, low power consumption FPGAs are available for the optimisation of the system.

#### 2.3.1 Related work

The field of FPGA-based frame grabbers for image processing has been under constant development during the last times. There are references of fully operating systems from more than ten years ago, developed with the technology constraints of those times, such as memories of only 1MB to store the images and bit resolution of only 8 bits [16]. However, the design principles underlying these obsolete systems are perfectly transferrable to current technologies, what can lead to greater designs.

This is the case of the work developed by Pierre Greisen et. al.[17], who developed a frame grabber aimed to create stereo vision video (3D imaging) taking the video streams of two cameras, and getting to a performance of a 30 fps frame rate with an image resolution as high as 1080p (1920x1080). This system was based in an Altera Stratix III FPGA in conjuction with a DRAM memory, transferring the data to the final computer by means of PCI Express communication standard.

Georgoulas et. al. [18] presented a frame grabber based in an Altera Stratix IV FPGA, also receiving two video streams from two different cameras in order to create an stereo vision video. The modules design within the FPGA are able to create the signals for the three dimensional recreation with a resolution of 1280x1024 at a frame rate of 251 fps. However, the system does not present a transmission method, what would more than likely suppose a bottleneck in the output frame rate.

Mateusz Michalak et. al. [19]. developed a frame grabber for a digital progressive scan image sensor, based in a Xilinx Spartan 6 FPGA. Using only two internal block RAMs, this system is able to transfer frames to the final endpoint with a resolution of 720p (1280x720) at a rate of 60 fps, by means of a HDMI output.

Apart from the stated ones, there are several technological developments on this field but, regrettably, they are all clearly too complex for a MSc project. Therefore, they are not a great target to follow for this project, but they do mean a great reference for demonstrating that the development of a FPGA-based frame grabber is perfectly feasible, and they give a view of the different equipment and communication systems usually selected for performing the operation.

In all these frame grabber systems, the communication standard is usually a bottleneck in the system, which, being based in FPGAs that work with high frequency clocks, can perform their operation at rates out of the reach of many communication standards. For this reason, the selection of an appropriate communication standard is crucial for maximising the performance of the whole system.

#### 2.3.2 Alternatives

It is also worth to consider the option of implementing the frame grabber in alternative and more traditional platforms, such as microprocessors or microcontrollers. However, although it might be possible to implement a frame grabber system in this kind of platforms, there are some issues making this option unsuitable.

Firstly, this kind of platforms are not prepared to deal with strict timings, which is absolutely mandatory for a frame grabber that needs to be adapted to the clearly defined and high speed communication protocol of any camera. In fact, due to the constraints in the protocols of the cameras, digital communication signals must be typically controlled with maximum accuracy, managing them in every clock cycle, which can be only achieved with a FPGA.

Secondly, although it might be possible to work at bit level in microprocessors, they are not aimed for this purpose and it would require the use of low-level languages that would make such a complex design quite difficult to be implemented. On the contrary, FPGA devices are directly designed for this purpose, and HDL languages, which are also low-level languages, are able to deal with bit level operation in a much more convenient way.

In fact, there is a wide catalogue of commercial frame grabbers available in the market, and all of them are based in FPGA. Regarding the suitability of the

commercial frame grabbers, they include all the necessary hardware for building a high performance frame grabber, offering different alternatives, especially in terms of communication interfaces. Thus, choosing the appropriate frame grabber board, the designer can optimise the operation of the imaging system. However, although manufacturers might provide some predesigned functions to deal with certain aspects of the frame grabber's operation, the final development of the system must be done by the designer.

On the other hand, once the decision of developing the frame grabber in base to a FPGA is made, many evaluation boards available in the market offer interesting features with a price typically lower than the commercial frame grabbers. Evaluation boards are electronic cards that, based in a certain FPGA, include a great deal of generic peripherals, such as memories (SRAM, DRAM, ROM...), SD card slots, displays, communication interfaces (RS-232, HDMI...) etc. Thus, the design of a frame grabber system can also be implemented with this kind of equipment, being able to give a good performance with a more reduced budget.

# 2.4 Communication standards for image transmission

When selecting the most suitable frame grabber, the communication standard that it uses for transmitting the data to the computer after collecting it from the camera is usually the main factor to be considered. There is a wide catalogue of commercial frame grabbers, based mainly in the following standards:

# 2.4.1 SDI (Serial Digital Interface):

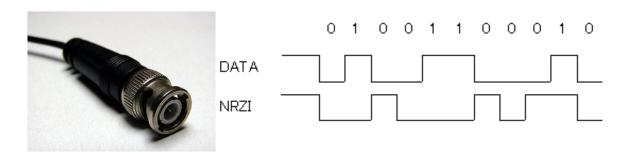

Standards used for the transmission of uncompressed and unencrypted digital video signals, by means of coaxial wires with BNC connectors (see Figure 2-5). For the data transmission, NRZI (Non Return to Zero Inverted) codification is used: either positive or negative voltages for every bit (not neutral state available) with level transitions only when a certain logical level (either 0 or 1, depending on convention) is detected in the next bit. An example of level transition with low level bits in shown in Figure 2-5.

Figure 2-5. BNC connector and NRZI codification example (image taken from [20])

Since the first SDI standard was introduced, multiple versions have been developed, with new and higher bitrates. They are shown in Table 2-1, along with their bitrates and most representative video formats [20]:

Table 2-1. SDI standards

| Standard                      | Bitrates (Gbit/s) | Video format |

|-------------------------------|-------------------|--------------|

| SMPTE 259M (SD-SDI)           | 0.27, 0.36        | 480i, 576i   |

| SMPTE 344M (ED-SDI)           | 0.54, 0.36        | 480p, 576p   |

| SMPTE 292M (HD-SDI)           | 1.485             | 720p, 1080i  |

| SMPTE 372M (Dual Link HD-SDI) | 2.970             | 1080p60      |

| SMPTE 424M (3G-SDI)           | 2.970             | 1080p60      |

| SMPTE ST-2081 (6G-SDI)        | 6                 | 2160p30      |

| SMPTE ST-2082 (12G-SDI)       | 12                | 2160p60      |

The resolution of the video format allowed for each standard is directly proportional to the maximum bit rate allowed, with displays resolutions from 640x480 pixels in the case of 480i (with typical display resolution of 640x480) to 3840×2160 pixels for 2160p standards (commonly known as 4K UHD).

#### 2.4.2 HDMI (High Definition Multimedia Interface):

Proprietary standard owned by HDMI Licensing LLC used for the transmission of uncompressed video (and compressed or uncompressed audio), implementing the interoperability standards created in CEA (EIA/CEA-861x) [21]. There are five variants of the HDMI connector, offering either increased resolution or reduced size (for portable devices) comparing to the original one. Some of them are shown in Figure 2-6:

Figure 2-6. HDMI connectors (image taken from [22])

Regarding the versions, up to 6 have been developed since HDMI was introduced, with different capabilities in terms of throughput and resolution, among others. Not all the features of a certain version are always implemented in the devices, but some variations are usually made. Focussing only in the maximum throughput of each version, the classification of the version could be made as presented in Table 2-2 (only useful throughput, the actual one is a 25% higher since every 8-bit colour signal rides in a ten-bit word, with 2 bits of overhead):

Table 2-2. HDMI versions

| Version  | Bitrate     |

|----------|-------------|

| HDMI 1.0 | 3.96 Gbit/s |

| HDMI 1.1 | 3.96 Gbit/s |

| HDMI 1.2 | 3.96 Gbit/s |

| HDMI 1.3 | 8.16 Gbit/s |

| HDMI 1.4 | 8.16 Gbit/s |

| HDMI 2.0 | 14.4 Gbit/s |

# 2.4.3 USB (Universal Serial Bus):

Standard initially developed for the communication and power supply between computers and peripherals, which nowadays is used for every kind of devices. The typical USB connector is shown in Figure 2-7:

Figure 2-7. USB connector (image taken from [23])

Once again, focusing the classification in the data rate offered by each USB version, the different version of USB can be sorted as in Table 2-3 [24]:

Table 2-3. USB versions

| Version | Bitrate    |

|---------|------------|

| USB 1.0 | 12 Mbit/s  |

| USB 2.0 | 480 Mbit/s |

| USB 3.0 | 5 Gbit/s   |

| USB 3.1 | 10 Gbit/s  |

#### 2.4.4 GigE (Gigabit Ethernet):

Being part of the Ethernet family of communication standards, Gigabit Ethernet can provide data rates of up to 1 Gbit/s while maintaining compatibility with systems of the same family deployed over the last three decades [25].

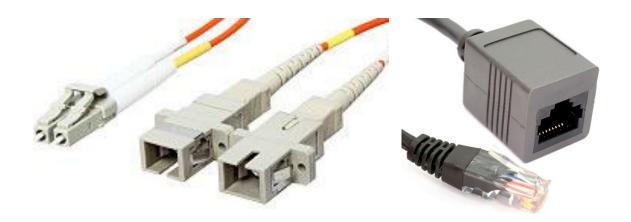

There are two variants within the GigE standard, each including different versions. The first variant to be released by IEEE, called 1000Base-X, was already capable of providing data rates of 1 Gbit/s, carried on optical fibre. Afterwards, aiming to take this technology to the desktop connection market, IEEE resealed the other variant of the standard, called 1000Base-T. This new version provides a new transceiver type to allow operation of GigE over the traditional UTP (copper lines), using digital signal processing techniques to compensate attenuation, distortion and the effect of crosstalk coming from other pairs within the same cable [25]. Thus, the challenge of getting the same data rate over copper lines as transmitting over optical fibre (1 Gbit/s) is overcome.

The connectors and sockets both variants are shown in Figure 2-8:

Figure 2-8. Connectors and sockets of 1000Base-X (left, optical fibre) and 1000Base-T (right, UTP) (image taken from [26])

## 2.4.5 PCI Express (Peripheral Component Interconnect Express)

Presented as an evolution of PCI standard, PCI Express offers a number of improvements comparing to the original PCI.

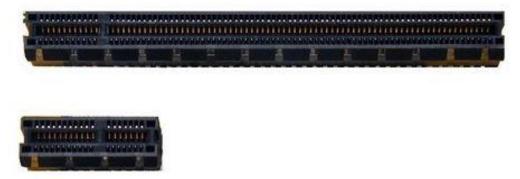

The operation protocol of PCI express is based in a complex system of layers, where the physical layer is composed of a variable number of transmit and receive pairs (called lanes). The physical layer can provide x1, x2, x4, x8, x12, x16 or x32 lane widths depending on the number of lanes used in each system, splitting the data to be sent among these lanes [27].

Thus, in the case of the first version of PCI Express, being each lane able to give a data rate of 250 MB/s and taking into account that each byte is encoded in a 8b/10b format, the useful data rate achievable with an only lane is up to 200 MB/s per lane. That is, a single lane in the first version of the system was already able to transfer useful data at 1.6G bit/s. Then, this data rate can be multiplied increasing the number of lanes up to 32 [28].

In the case of following versions of PCI Express, the encoding scheme was improved, reducing the number of overhead bits in each transfer, and increasing the data rate of each lane.

The capabilities of each version is shown are shown in Table 2-4, stating the maximum data rate in terms of useful data (after removing overhead bits) for x1, x16 and x32 lane widths as a reference [28]:

Table 2-4. Versions and data rates of PCI Express

| Version | Encoding<br>System | I      | Data Rate (Gbit/s | s)       |

|---------|--------------------|--------|-------------------|----------|

|         |                    | 1 lane | 16 lanes          | 32 lanes |

| 1.0     | 8b/10b             | 2      | 32                | 64       |

| 2.0     | 8b/10b             | 4      | 64                | 128      |

| 3.0     | 128b/130b          | 7.8    | 126               | 252      |

As it can be noticed in the table above, this communication system is hugely powerful in terms of throughput, offering also a great flexibility due to the variable number of lanes. However, the implementation of this system is also very complex, what makes it very unreachable for this MSc project.

Two PCI connectors are shown in Figure 2-9. PCI Express x16 (top, 164 pins) and PCI Express x1 (bottom, 36 pins) connectors Figure 2-9:

Figure 2-9. PCI Express x16 (top, 164 pins) and PCI Express x1 (bottom, 36 pins) connectors (image taken from [29])

#### 2.4.6 RS-232:

Being the most common standard for serial transmission of data, its transmission rate is not defined in the standard (although it states that it is intended for data rates lower than 20 kbit/s) [30].

In serial communications, TTL voltage levels (internal levels of the digital electronics systems) are represented by ground level for logical 0 and Vcc level (power supply voltage of the system, typically 3.3V or 5V) for logical 1. On the other hand, RS-232 standard uses two voltage levels: -3V to -15V for logical 1 and 3V to 15V for logical 0. For this reason, when implementing a serial communication it is necessary to convert the signal levels from TTL to the chosen serial standard level. The chip in charge of this conversion is precisely the most important component involved in a digital system performing a RS-232 communication, and it is the key factor for determining the data rate of the system using the serial standard.

Although not being stated in the standard itself, it is widely known that, with appropriate hardware, RS-232 can perform data rates far beyond its initially

targeted value of 20 kbit/s. Thus, with a high performance converter, data rates of up to 2 Mbit/s can be achieved [31].

The greatest advantage of serial RS-232 standard is the ease for implementing it in a digital system. It includes some control signals for the communication, but only the TxD (transmission) and Rxd (Reception) lines are essential. Thanks to this simplicity, a RS-232 communication can be implemented in a FPGA by means of a serial transmission module, which sets the value of a certain output pin of the system alternatively to either logic 0 or 1 every period of the maximum frequency allowed, and a serial reception module, which "listens" to a certain input port to sample the received bits.

Figure 2-10 shows the typical DB9 connector used for RS-232 communications:

Figure 2-10. DB9 female (left) and male (right) for RS-232 communications (image taken from [32])

#### 2.4.7 RS-422

Standard compatible with the RS-232 version, being the use of differential signalling in RS-422 the main difference between them, this standard is especially robust for long distance transmission in noisy environments [33].

In differential signalling, a signal is sent over a pair of wires attached one to the other with opposite polarities. The resonant effect caused by the crosstalk noise might affect the quality of the signal [34], but thanks to the closeness of both differential wires they will presumably be affected in the same way, what means

that the voltage level between them should not be affected. Thus, decoding the values of a bit stream by means of the difference between the positive and the negative wires, the differential signalling gives a greater reliability compared to serial communication of bits with a single line. Thanks to this fact, RS-422 gives a greater reliability against errors in the transmission line compared to RS-232, allowing the serial communications to be performed over longer distances and with higher bit rates [35].

In the same way as RS-232, the RS-422 standard does not define the bit rates achievable with its use. However, with appropriate hardware, the standard has been proved to perform with a data rate of 10 Mbit/s over distances of 1200m [33].

RS-422 standard can be implemented using the same connectors as RS-232. For this purpose, two of the pins used for control signals must be used for the extra lines needed for the differential transmission of data.

# 2.5 Summary

The field of frame grabbers for image processing has been under constant development for the last decades. The operation of these devices can be separated in two separated stages:

- The process of collecting the video frames from the camera, saving them in the memory of the frame grabber and finally forwarding them to the computer (final endpoint).

- Once the frames are saved in the memory of the frame grabber, apply different image processing techniques to them.

The first stage is mandatory for any frame grabber, whilst the second one is dependent on the final application of the system. Due to the tight time constraints, the target for this MSc thesis is to develope a frame grabber that effectively collects and forwards video frames without processing them.

Being gas sensing the application field initially aimed, there is a wide range of applications demanding a frame grabber for collecting and processing video frames. Some of these are image monitoring of pick and place machines in manufacturing, medical imaging and stereo video (three-dimensional imaging).

The use of FPGA devices for the development of frame grabbers is the most suitable option, since it reduces the latency between frames thanks to its parallel implementation capability and high frequency operation. Besides, it is essential to operate at bit level and to manage the timings of the system in order to synchronise it with the protocol of each camera, which can only be done with an FPGA. A good proof of the suitability of FPGA devices for building frame grabbers is the large amount of previous work in the field and the commercial frame grabbers currently available, which are all based in FPGAs.

The throughput of the system is usually limited by the communication standard used for the transmission of the data from the frame grabber to the computer. Therefore, the selection of this standard is the most delicate issue to manage in the preliminary work. The maximum data rates achievable with each standard are shown in the Table 2-5:

Table 2-5. Summary of data rates of the main communication standards used in frame grabbers

| Standard                   | Maximum data rate (Gbit/s) |

|----------------------------|----------------------------|

| SPI (SMPTE ST-2082)        | 12                         |

| HDMI 2.0                   | 14.4                       |

| USB 3.1                    | 10                         |

| Gigabit Ethernet           | 1                          |

| PCI Express 3.0 (32 lanes) | 252                        |

| RS-232                     | 0.002                      |

| RS-422                     | 0.01                       |

Regarding the difficulty of implementation, serial protocols are clearly the simplest ones. Among these, RS-232 is the simplest one because it only needs a transmission and a reception line to be implemented.

# 3 DESIGNED SYSTEM

# 3.1 Preliminary decisions

After the exhaustive research on the field done in the literature review, and taking into account other factors external to the project itself, such as the time available for the project and the background of the designer, the main decisions for the design are made.

First, considering the design based in FPGA as the only suitable option, the frame grabber system is decided to be implemented in an evaluation board instead of a commercial frame grabber. There are a few heavy reasons for this. The equipment of evaluation boards is far enough to achieve the targeted features, being cheaper than a commercial frame grabber with specialised hardware. Commercial frame grabbers are clearly oriented to the development of high performance systems, and the frame grabber needed for this project does not need such powerful features. Furthermore, the Group of Engineering Photonics of Cranfield University, where the project is developed, has experience in the use of a certain evaluation platform. This could undoubtedly mean a great asset, since the support of experienced designers could make a difference in case of getting to unforeseen difficulties.

Secondly, the camera outputs the images data in analogue format. Therefore, the FPGA will need to make use of an ADC peripheral for digitalising the analogue signal but, regrettably, this is not included in the selected evaluation board. For this reason, an external board compatible with the evaluation board is needed to perform this operation.

Finally, the most problematic point is addressed: the communication system used for the transmission of images from the frame grabber to the computer. As stated earlier in Section 2.3.1 (Related work), this is always a potential bottleneck for the system, and can convert a fast operating system into a slow system. However, the communication is very critical for the frame grabber, not only in terms of performance for the final system but also for the constant debugging that will be needed during the development. As a consequence, it is

paramount to deal with this issue as quickly as possible, in order to have time to develop the core of the frame grabber.

In this context, serial communication standards are clearly the easiest options. Then, RS-232 is selected because it does not require differential signalling, what would be an extra difficulty. Besides, USB capable RS-232 chips are widely available, making the connection to the PC very simple without any signal conditioning or amplification, as it would needed in RS-422. In order to facilitate the substitution of this communication standard in the future (once the frame grabber operation is validated) the transmission process performed by the serial line is thought to be set apart from the rest of the design.

# 3.2 General Description of the system and Equipment

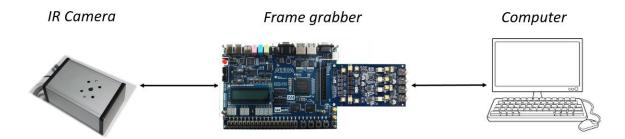

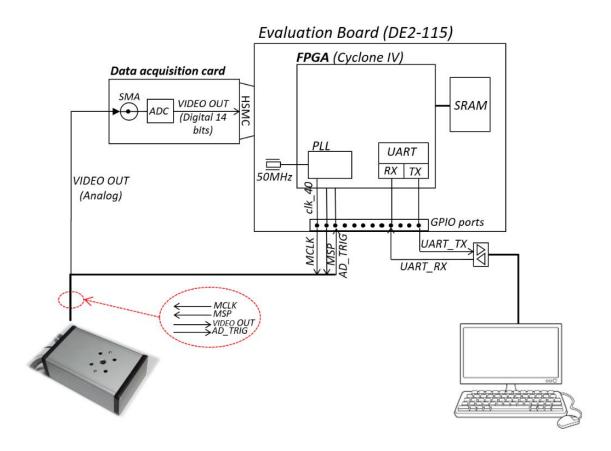

The whole IR imaging system could be divided in three main parts: the Hamamatsu sensor (the IR camera), the computer where the IR images captured by the camera will be saved and displayed, and the electronic system allowing this operation between both endpoints, the so-called frame grabber. This basic view of the system is shown in Figure 3-1:

Figure 3-1. Overview of the IR imaging system

The work of this thesis is principally focused in the design and development of the frame grabber, although some time was also invested in the development of the Matlab scripts needed for taking the raw data from the frame grabber in the computer and then building the images from this data.

## 3.2.1 The Hamamatsu Image Sensor (G11097-0606S)

It provides 64x64 pixels infrared images, captured by means of a series of InGaAs photodiodes (one per pixel) with a spectral response range (wavelengths captured) from 0.95  $\mu$ m to 1.7  $\mu$ m. Each pixel's dimension are 50x50  $\mu$ m, with a pixel pitch (distance between two adjacent pixels' centres) of 50  $\mu$ m, what means an overall image size of 3.2x3.2 mm. The Hamamatsu Imaging Sensor is shown in Figure 3-2:

Figure 3-2. Hamamatsu sensor (image from [36])

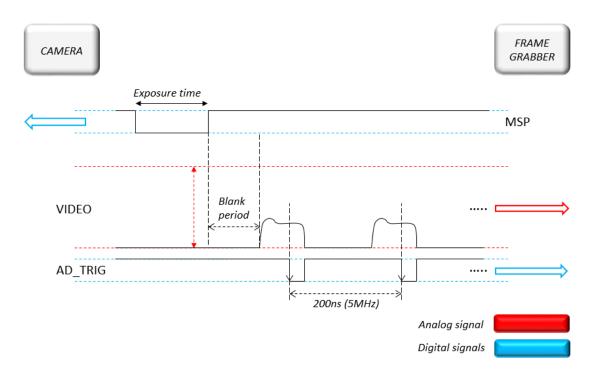

The captured pixels are transmitted by means of an analogue video output, which is triggered with a digital signal and easily obtained by just supplying a master clock and master start pulse from external digital inputs [36].

It is extremely important to understand this operation, since the whole system is based on these control signals. The signals involved in this communication are listed below:

- MSP (Master Start Pulse, digital input): also called integration signal, it is used for indicating the camera when it should start the process of capturing and sending an image. This order is given to the camera by means of a low level pulse in the signal. As soon as the camera detects a low level in the MSP input, it starts capturing a new image, and keeps the lens capturing until the MSP input is released (until it comes back to high level). Therefore, the duration in time of the MSP low pulse, the so-

called integration time, states the exposure time for capturing the new frame.

- MCLK (Master Clock, digital input): the reference clock for the camera, up to 40 MHz.

- VIDEO (video signal, analogue output): Right after the end of the image capture, the camera starts to send the pixels' analogue values, one by one, throughout the analogue VIDEO output at a frequency rate of up to 5 MHz (the frequency of the clock divided by 8). It is important to highlight that this is an analogue signal and, therefore, it needs to be digitalised in order to be received in the FPGA.

- AD\_TRIG (trigger, digital output): this video trigger digital output is given

to the frame grabber along with the VIDEO analogue output, and

provides a falling edge every time a new pixel value is stable to be read.

The transmission process is arranged in an accurate way, alternating pixels' transmission with a set of blank spaces, previous to the first pixel of the frame, after the last one and between rows of the image (blank spaces after each set of 64 pixels). This is illustrated in Figure 3-3, which is a timing diagram taken from the datasheet of the IR camera:

Figure 3-3. Timing diagram of the camera's signals (image taken from [36])

## 3.2.2 The frame grabber

It is the electronic system in charge of controlling the whole imaging system. It allows the configuration of the operation mode and other parameters from the computer, and afterwards it takes the images from the camera for sending them to the computer. It is designed with two different operation modes, plus a third mode for calibration purposes:

- 1. Live mode: it takes a frame from the camera, saves it in a SRAM and sends it to the computer. It repeats this process iteratively, creating a real time video stream to be displayed in the computer.

- Buffer mode: it captures at very high speed a certain number of images, storing them all in a SRAM. Once finished taking the images from the camera, it transmits them all to the computer.

- 3. Calibration mode: it takes up to 25 consecutive values of the digitalised VIDEO signal around the falling edge of the trigger signal, in order to calculate the delays between both signals. It is used for the calibration of the system, making possible to find the perfect moment to capture each pixel.

For the development of the frame grabber, two electronic boards are used:

1. Altera DE2-115 Evaluation Board: based in an Altera Cyclone IV FPGA, where the main part of the frame grabber will be implemented by means of VHDL language. It also includes different peripherals needed for the operation of the system, such as a SRAM, GPIO ports or a HSMC connector for plugging a data acquisition card that will allow the digitalisation of the analogue data coming from the camera. The DE2-115 board is shown in Figure 3-4:

Figure 3-4. Altera DE2-115 Evaluation Board (image taken from [37])

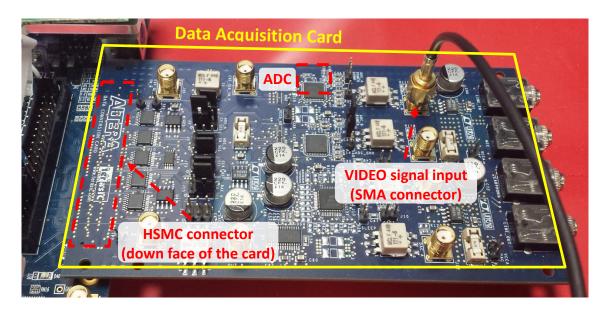

2. AD/DA Data Conversion Card: this is the Data Acquisition Card, equipped with the ADC used remotely by the FPGA to digitise the analogue data coming from the camera in order to process it. The board is shown in Figure 3-5:

Figure 3-5. AD/DA Data Conversion Card (image taken from [38])

## 3.2.3 Computer

No major developments were needed for the computer. The data is transmitted from the frame grabber to the computer using the RS-232 standard, and the configuration of the frame grabber is set sending the parameters to the frame grabber using the same standard. For this purpose, a Serial Protocols emulator (Docklight) was used. Apart from this, a Matlab script for decoding raw the data coming from the frame grabber and building the final images from this data was developed.

#### 3.2.4 Other hardware

The IR camera could not be connected directly to the Evaluation Board and the Data Acquisition Card. Some adaptation work must be done first. On the one hand, the voltage levels of the signals for the communication between the camera and the frame grabber need to be adapted to the inputs of the frame grabber. This is managed in an adaptation board attached to the image sensor.

On the other hand, some aspects which are secondary for the communication but essential to allow camera's operation, such as power supply and temperature control, must be also managed with a great deal of care. For this purpose, the camera is connected to another board. The main blocks of the resulting system are shown in the diagram of Figure 3-6:

Figure 3-6. Blocks diagram of the adaptation of Hamamatsu imaging sensor to the overall system

First, the board for power supply and temperature control is packed in a box separated to the test of the system. This box is connected to the electrical power supply of the laboratory, using this to create the voltage levels needed to power up the camera. Besides, it also performs the needed temperature control mechanisms using the signals provided by the camera for this purpose<sup>1</sup>.

Regarding the adaptation board, in the Digital Signal Level Translators it converts the voltage levels of the digital signals of the camera to the levels needed in the frame grabber. The Video Buffer, which is an amplifier configured for an amplification of 1, decouples the VIDEO output from the Hamamatsu module from the cable and receiver.

Then, both the camera and the adaptation board are packed into a protective case, getting to the box shown in Figure 3-7. The box includes 4 holes around the image sensor that will be used for fixing a system of lenses for getting images once the frame grabber is working.

Figure 3-7. Protective case containing the IR camera chip and the adaptation board

\_

<sup>&</sup>lt;sup>1</sup> All the adaptation work was done by Dr Steve Staines and Dr Thomas Kissinger

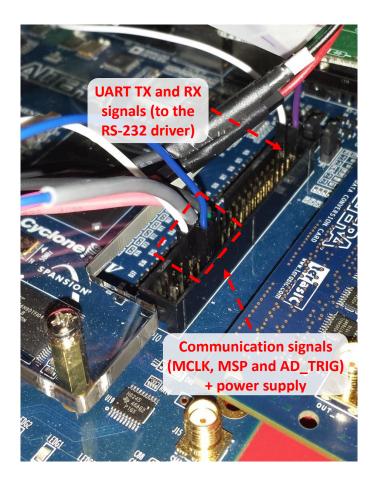

Regarding the communication between the frame grabber and the computer, although the DE2-115 includes the DB9 connector typically used for RS-232 communications, another external small platform is used. The serial communication lines (TX and RX) of the system are mapped to the GPIO ports of the Evaluation Board, and these are connected to the external platform. Thus, thanks to the high speed driver included in this platform for the conversion of the signals coming from the FPGA (TTL) to RS-232 levels, the serial data transmission is increased to a rate of 1 Mbps. If needed, this driver could operate at a rate of up to 2 Mbps. The external platform for TTL to RS-232 conversion is shown in Figure 3-8:

Figure 3-8. External platform affixed in a corner of the Evaluation Board

As seen in the picture, the driver is directly connected to the PC by means of a micro-USB cable.

# 3.3 Architecture of the IR imaging system

The general architecture of the overall system is shown in Figure 3-9:

Figure 3-9. Architecture of the IR imaging system

As stated above, there are two endpoints in the overall imaging system: the camera (shown at the left of image) and the computer (shown at the right).

The control and data signals from the camera are listed in the red ellipse, connected to the frame grabber after the adaptation explained in Section 3.2.4 (Other hardware). In the particular case of the VIDEO output analogue signal, the adaptation board outputs it over a coaxial cable. Thus, the signal is received in the Data Acquisition Card through its SMA connector, passing it to the ADC. In the ADC, the analogue signal is digitalised into a 14 bits digital signal, which

is transmitted to the Evaluation Board by means of the HSMC connector. These connections are shown in Figure 3-10:

Figure 3-10. Connections in the Data Acquisition Card

Once the digital VIDEO output is introduced in the Evaluation Board, it is easily received in the FPGA to process it. The value of the analogue VIDEO output is digitalised and transmitted to the FPGA every clock period. This is the reason why the AD\_TRIG signal is very important, because it states when the VIDEO data is giving the value of a pixel, once every 8 clock cycles.

Regarding the control signals of the camera, which are already digital, they are directly connected to the GPIO ports of the Evaluation Board (see Figure 3-11). One of those signals is MCLK, the reference clock provided to the camera, which should be not faster than 40 MHz. However, the oscillator of the Evaluation Board provides the system with a 50 MHz clock. For this reason, it is necessary to implement a PLL within the FPGA in order to create the 40 MHz clock needed for synchronising the whole system.

Figure 3-11. GPIO ports connections

Once inside the FPGA, the pixels data coming from the VIDEO output of the camera are saved in the SRAM included in the Evaluation Board. Afterwards, depending on the operation mode, this data is processed in diverse ways, being always read from the SRAM and sent to the computer through the UART module, which is implemented within the FPGA.

Finally, the data managed by the UART module is converted to RS-232 levels. The UART module is used for both transmitting the video data to the computer and for receiving the configuration parameters from the computer before starting the data transmission.

# 4 DEVELOPMENT OF THE SYSTEM

The development of the system has been divided in four different stages, which are formed by several subtasks:

- Building Blocks.

- Developing a basic version of the system able to capture an only frame and to transmit it to the computer.

- Creating the Live and Buffer operating modes, based in the previous basic version.

- Adapting the design to the actual camera, including the creation of the third operation mode, the Calibration Mode.

In this section, the most important aspects of the development are stated, along with the technical details involved in each of the stages.

# 4.1 Building Blocks

Provided the great deal of hardware involved in the design, before starting the development of the system, it was important to have a clear view of the operation of every single component. For this reason, the next modules were developed:

#### 4.1.1 SRAM read/write module.

A basic module for testing the operation of the memory that would be used for saving the pixels as they are received from the camera, and to read this data in order to transmit it to the computer. This might look an easy task, but there are a few signals to deal with, and the operation protocol is not stated anywhere. For this reason, it was necessary to invest some time in this apparently simple module.

#### 4.1.2 UART modules.

Including both data reception and transmission modules, the development of this modules was paramount for the communication of the frame grabber with the computer, for both receiving the configuration parameters from the computer and sending the images' data to the computer<sup>2</sup>.

# 4.1.3 Mirror test for the Data Acquisition Card (ADC and HSMC connection test).

For testing the operation of the Data Acquisition Card, although only the ADC of the card was supposed to be used in the final design, a mirror test involving both the ADC and DAC was performed. This test was, basically, inputting to the ADC an analogue signal directly created with a functions generator, receiving the digitalised data in the FPGA by means of the HSMC connection between the Data Acquisition Card and the Evaluation Board, and finally outputting the signal in the opposite way. That means, sending the digitalised signal received in the FPGA back to the Data Acquisition Card through the HSMC connection, this time to the DAC, which would convert the signal from digital to analogue again and output it from the system. This mirrored signal is analysed with an oscilloscope, which plots the signal with the same shape as the signal generated by the functions generator.

# 4.1.4 Hamamatsu Debug Module.

Due to a delay in the delivery of the Hamamatsu image sensor, the operation of the frame grabber could not be physically tested until the last stage of the thesis. During the first stages of the design, all the process was tested and debugged by means of the simulation tools provided for the FPGA. Regrettably, only the operations performed within the FPGA could be analysed with this method, and provided that the system manages some external peripherals, the final operation of the whole system could not be tested by means of the simulation. Therefore, it was necessary to find a mechanism to perform a physical debug of the system. Thus, a module that recreates the operation of the camera was developed in VHDL code and integrated within the FPGA. The pinout of the module, which includes the signals presented in Section 3.2.1, is shown in Figure 4-1:

<sup>&</sup>lt;sup>2</sup> UART RX module based in a previous work by Dr. Thomas Kissinger

# Hamamatsu Debug CLK AD\_TRIG VIDEO

Figure 4-1. Pinout of the Hamamatsu Debug Module

This module performs a communication with the frame grabber system (implemented both endpoints within the FPGA), based in the operation protocol used by the actual IR camera. The module recreates only the signals of the camera that are involved in the communication process (MCLK, MSP, VIDEO and AD\_TRIG), ignoring the signals dealing with secondary aspects (power supply and temperature control).

The main constraint of this physical debugging method is that, due to the impossibility of recreating the analogue VIDEO signal within the FPGA, the digitalisation of the signal by means of the Data Acquisition Card cannot be tested this way. Therefore, the VIDEO signal is provided as it would be after the digitalisation, with a digital bus of 14 bits. As real values are not needed for the debug, a sequence of numbers from 0 to 4095 (for the 4096 pixels of the image) is given as each image's pixels values.

Thanks to the mirror test performed for testing the correct operation of the Data Acquisition Card (see section 4.1.3), this part of the system is considered to be a non-problematic factor to be implemented afterwards in the final version of the system, once the camera is available.

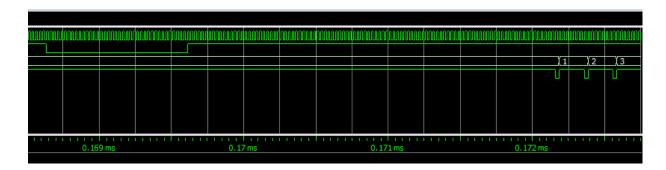

The operation of this VHDL module is shown in Figure 4-2, which gives a view of the simulation of the behaviour of the module when it receives the MSP signal:

Figure 4-2. Simulation of the Hamamatsu Debug Module

In this simulation it is shown how the Hamamatsu Debug Module receives the MSP low pulse (second line) and waits for the first blank period to expire before starting to send the pixel values (the increasing sequence in the third line, already in digital format). It gives a falling edge in the AD\_TRIG (fourth line) in certain points where the value of the pixel is supposed to be stable.

#### 4.2 Basic version

Once all the peripherals of the system have been tested, the first basic version of the system is developed. This is the first stage in the actual development of the system and, provided that all the posterior design is based upon this first basic version, it is also the most important stage.

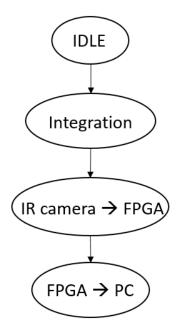

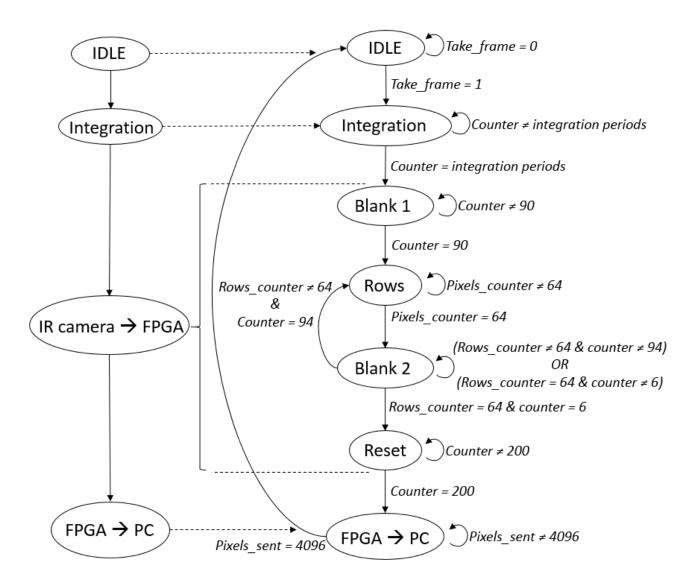

The first point in this development is to define the flow diagram of the system, which is transferred to the finite-state machine within the FPGA. The finite-states machine will rule the operation of the system according to the timings set by the camera's operation protocol. A basic representation of the flow diagram is presented in Figure 4-3 (for further details, see the full flow diagram in Appendix A (Flow Diagrams):

Figure 4-3. Flow diagram of the basic version of the system

The operation of the basic system is based in three main stages: integration time, collecting the data from the camera in the frame grabber and sending the collected data to the computer. In the first state (IDLE), the system is simply waiting for the order from the user to start the process, order that it receives when a button of the Evaluation Board is pressed.

#### 4.2.1 Integration Time

The first step in the operation of the imaging system. The only action performed in this state is setting the value of the MSP signal to 0. Thus, the time this state is run sets the exposure time for the capture of the image by the camera, which in the basic version of the system is a fixed value. The capture of the image by the camera ends right in the same moment in which the MSP comes back to high level.

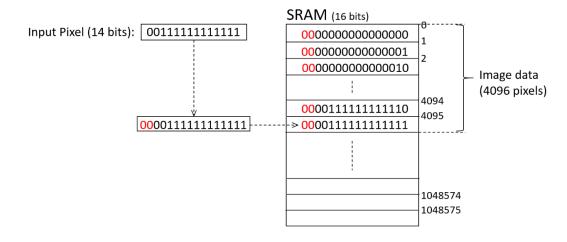

# 4.2.2 Collecting the image's data in the frame grabber

After capturing the image, the camera waits for a certain blank period of time to expire and then starts to send the pixels one by one through the VIDEO output analogue signal to the frame grabber, along with the AD\_TRIG trigger signal. A

schematic view of this process is given in Figure 4-4, with only the first two pixels out of 4096 in each image represented in the diagram:

Figure 4-4. Beginning of the communication between the camera and the frame grabber

Every falling edge of the AD\_TRIG, a new pixel value is taken in the FPGA. This value is aimed to be a digitalised version (14 bits) of the analogue VIDEO output of the camera, but in the first stages of the development this 14 bits value will be directly taken from the Hamamatsu Debug Module's VIDEO digital output.