CAMPUS OF INTERNATIONAL EXCELLENCE

#### FACULTY OF ENGINEERING IN BILBAO Department of Electronic Technology UPV/EHU

#### DOCTORAL THESIS

#### Contributions to the design of power modules for electric and hybrid vehicles: trends, design aspects and simulation techniques

Author: Asier Matallana Fernández Supervisor: Dr. Jon Andreu Larrañaga

Bilbao, December 2019

(c) 2020 Asier Matallana Fernández

A los de casa, Amatxu, Aita y Amama. - Montse, Ovidio y Primi -

> Gracias Amatxu y Aita por estar siempre ahí, Amama seguro que lo estás viendo.

ii

### Agradecimientos

En primer lugar, y como es natural, me gustaría dar las gracias a mi amigo y director de tesis, Jon Andreu Larrañaga. Gracias Jon, por todos estos años de duro trabajo juntos. Comenzaron cuando fuiste mi profesor de Sistemas Digitales, después mi director de proyecto final de carrera y, por último, mi director de tesis. Espero que esta larga relación, tanto personal como profesional, continúe durante muchos más años. Aquí tienes un amigo.

Me gustaría dedicar también unas líneas a Iñigo Kortabarria, José Ignacio Garate e Iñigo Martínez de Alegría. Siempre me habéis ayudado en todo lo posible, escuchando mis dudas y problemas, e intentando buscar las mejores soluciones. Siempre me he sentido apoyado y respaldado, nunca solo.

Gracias Nicola Delmonte y Paolo Cova por acogerme en la Universidad de Parma y por todo el tiempo que me dedicasteis, fue un auténtico placer trabajar con vosotros. Mi estancia en la ciudad fue una gran experiencia profesional y personal y espero que podamos continuar trabajando juntos en un futuro.

Especial mención quiero que reciban mis compañeros y amigos Iraide López y Edorta Ibarra. No me olvidaré de vuestra ayuda incondicional en la última fase de este trabajo. Me habéis demostrado que sois grandes trabajadores y mejores personas.

Siempre recordaré a todos mis compañeros de despacho: Igor Villalta, Oier Oñederra, Itxaso Aranzabal, David Cabezuelo e Iker Aretxabaleta. Gracias por haberme escuchado durante todos estos años, aguantar mis cambios de humor y soportar mis chistes malos. Ha sido un verdadero placer compartir este tiempo con vosotros.

Por supuesto, no me quiero olvidar del resto de compañeros del laboratorio: Endika Robles, Markel Fernández, Ángel Luis Pérez-Basante, Julen Gómez-Cornejo, Naiara Moreira, Estefanía Planas, Víctor López y Uli Kretzschmar. Vuestros ánimos me han permitido seguir adelante en los malos momentos.

También quiero mencionar a mis compañeros de la Universidad de Parma: Simone Di Napoli, Martina Carrisi y Sergio Sapienza. Me ayudasteis en todo lo que pudisteis, haciendo que mi estancia fuera inolvidable.

Por último, no puedo olvidar a mis amigos: Iñigo, Alex, Bego, Joseba, Josu, Igor y Víctor. Siempre habéis estado apoyándome, escuchándome y aconsejándome, siento haber sido tan aburrido en tantas ocasiones. También guardo un especial recuerdo para la cuadrilla de la Residenza Cocconi: Daniele, Beatrice y Valentina. Fue increíble la experiencia en Italia.

Y, sobre todo, a Amatxu y Aita, por haber disfrutado mis momentos de alegría y euforia, y aguantado mis lloros y hundimientos. Permanecer unidos es lo que me ha permitido llegar al final. Misión cumplida, como le hubiese gustado a Amama.

En Bilbao, Diciembre de 2019.

#### Abstract

A large number of factors such as the increasingly stringent pollutant emission policies, fossil fuel scarcity and their price volatility have increased the interest towards the partial or total electrification of current vehicular technologies. This transition of the vehicle fleet into electric is being carried out progressively. In the last decades, several technological milestones have been achieved, which range from the development of basic components to the current integrated electric drives made of silicon (Si) based power modules. In this context, the automotive industry and political and social agents are forcing the current technology of electric drives to its limits. The technological targets proposed by Horizon 2020, USCAR, DOE and UN ESCAP regarding the power electronics are stringent, and can be summarized in the following items:

- 1. An increase of the power density of the power conversion stage of around 50 % (from 8.7 kW/l up to 13.4 kW/l).

- 2. A reduction of power converter losses (conduction and switching losses) by 50 %.

- 3. Significant costs reductions (a reduction by four) for on-board power electronics (from 30 \$/kW to 8 \$/kW).

- 4. Simplification of thermal management systems by using on-board coolants minimizing, as possible, the usage of additional components.

- 5. Whole drive size and weight reductions of 35 % and 40 %, respectively (from 1.1 kW/kg and 2.6 kW/l up to 1.4 kW/kg and 4.0 kW/l).

Specifically, the U.S. DOE's goals for 2020 propose the development of power converter technologies with specific power of more than 14.1 kW/kg and efficiencies greater than 98 %. At the same time, the aforementioned goals aim for a significant cost reduction up to 3.3/kW.

Thus, these goals encourage the development of the main parts of the traction system: battery, power converter and engine. The research line of this work is focused on the analysis and design of the power modules in order to improve their capabilities which are necessary to meet the aforementioned goals.

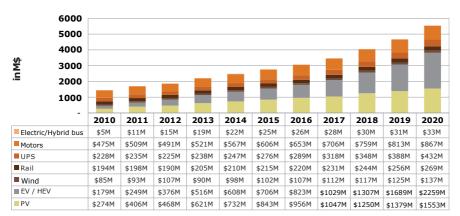

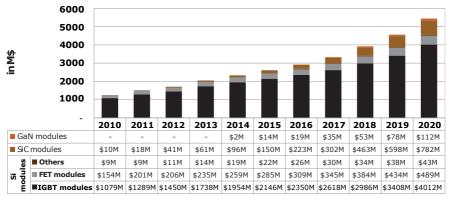

This thesis presents an in-deep review of the state of the art concerning its internal power semiconductors and many internal design aspects of power modules. According to semiconductor technology, *Wide bandgap* (WBG) semiconductors, and specially, silicon carbide (SiC) based power electronic devices, are identified as the most promising alternative to Si devices due to their superior material properties. In fact, the current silicon and WBG technologies are reviewed in this document and, after a market analysis, the most suitable power semiconductor devices are highlighted in order to be assembled inside a power module.

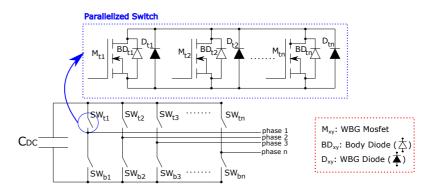

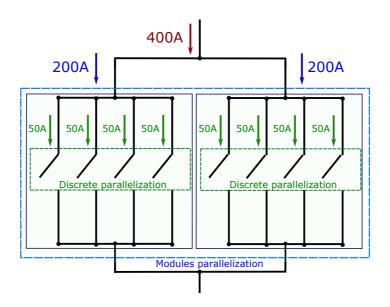

In addition to power semiconductor technology, the main concepts of electrical connections between devices, where the parallelization is required, are extracted in order to develop and propose some specific power module design criteria which ease this task. The main power module design concepts are identified through scientific, industrial and commercial literature taking into account the power module electrical requirements. These criteria allow routing correctly control and power signals with an optimum WBG-based die parallelization.

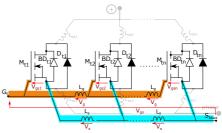

These proposed design concepts are put into practice and verified through three initial power circuits based on PCB substrate technology, where electrical cosimulations have been realised in order to extract circuit behaviour. These circuits are different parts of a power converter (power switch, half-bridge and DC-link) where a progressively parallelization and symmetry have been implemented at different levels. According to the electrical simulation results obtained, the alternatives with the highest integration of both concepts, the best voltage and current balances show.

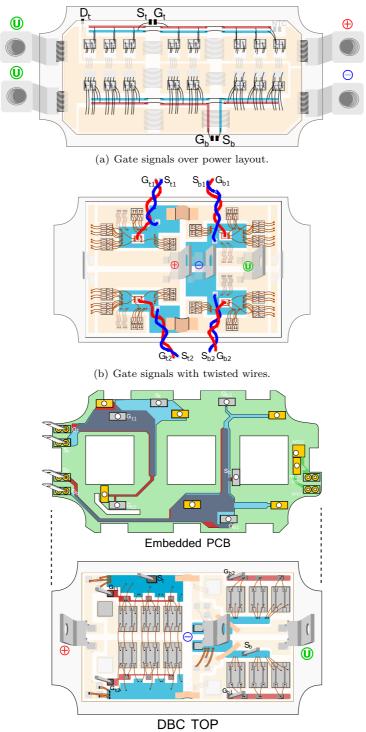

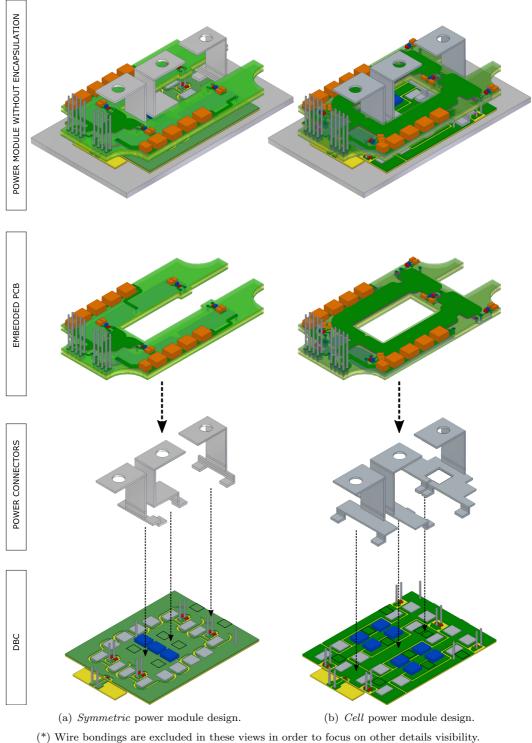

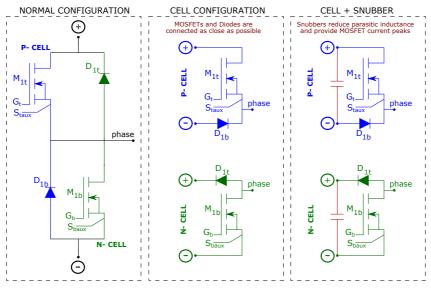

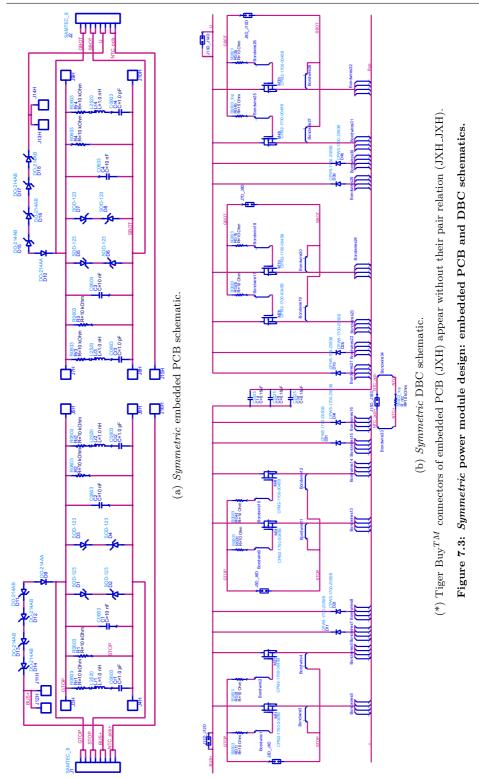

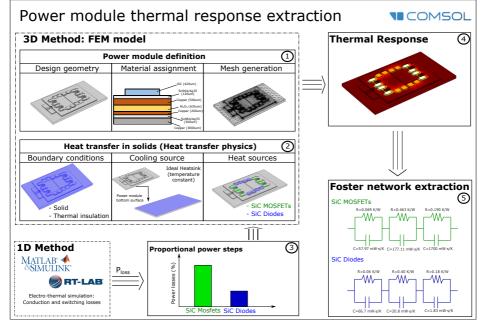

Finally, two power module proposals have been presented, called symmetric and *cell* designs. Both circuits are half-bridge topologies where the proposed design criteria have been implemented. In the symmetric design a much stricter symmetry concept has been applied than in the *cell* design where the connections are practically identical, thus affecting the current balance that flows through each power semiconductor. In the case of *cell* design, the main benefits are due to the semiconductor placement in a P- and N- cell configuration (MOSFETs and diodes are connected as close as possible in the switching loop) with snubber capacitors, reducing the length of electrical connections and balancing the circuit. The electrical co-simulations through  $ADS^{TM}$  software verified the effectiveness of the layouts according to the design criteria application. Apart from the electrical behaviour, the electro-thermal response of each power module has been

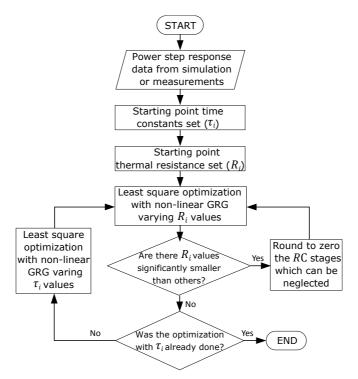

extracted in order to detect reliability issues. Thanks to a specific methodology developed in this thesis, which combines 1D and 3D simulation techniques, the power modules are evaluated thermally according to real operation conditions provided by driving cycle profiles. After the analysis of thermal data in each proposal, no critical points have been detected, avoiding reliability issues.

The electrical and thermal simulations verified the improvements of the proposed design criteria for the development of HEV/EV power modules. The results of this methodology improve the prototyping step since it starts with more information about design electrical and thermal behaviour.

#### Resumen

En la última década, la protección del medio ambiente y el uso alternativo de energías renovables están tomando mayor relevancia tanto en el ámbito social y político, como científico. Problemas derivados de los gases de efecto invernadero, el alto grado de polución en las ciudades, la escasez de combustibles fósiles y la volatilidad de sus precios son cuestiones que están acelerando el desarrollo de sistemas de energía renovables más eficientes y sostenibles.

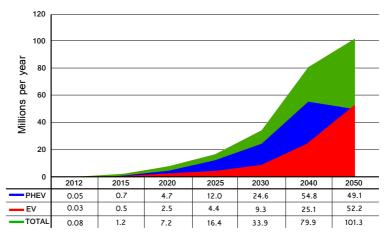

En este contexto, el sector del transporte es uno de los principales causantes de los gases de efecto invernadero y la polución existente, contribuyendo con hasta el 27% de las emisiones a nivel global. Dentro del sector de transporte (aéreo, ferroviario y carretera), el transporte por carretera supone el 75% de las emisiones, siendo este tipo de medio el principal causante del incremento de los niveles de contaminación. De acuerdo a las perspectivas de aumento de población, el parque de vehículos por carretera puede alcanzar los 200 millones de unidades en el año 2050. Por consiguiente, si se continua con la misma tendencia, se estima un alza de los niveles de polución entorno al 30% para dicho año. En este contexto desfavorable, la electrificación de los vehículos de carretera se convierte en un factor crucial para solventar y paliar los problemas sociales y medioambientales. Para ello, la transición de la actual flota de vehículos de carretera debe ser progresiva (estimación de 100 millones de unidades para el año 2050, según el IEA Energy Technology Perspective BLUE Map), forzando la investigación y desarrollo de nuevos conceptos a la hora de producir vehículos eléctricos (EV) y vehículos eléctricos híbridos (HEV) más eficientes, fiables, seguros y de menor coste.

Sin embargo, los retos y desafíos futuros son cada vez mayores. En este sentido, diversos organismos como Horizon 2020, USCAR, DOE y UN ESCAP han fijado las siguientes metas:

1. Incremento de la densidad de potencia de la etapa de conversión entorno al 50 % (de 8,7 kW/l a 13,4 kW/l).

- 2. Reducción de las pérdidas de potencia del convertidor del 50 %.

- 3. Reducción significativa (x4) de los costes de fabricación de la electrónica de potencia (de 30 \$/kW a 8 \$/kW).

- 4. Simplificación de los sistemas de refrigeración, minimizando el número de componentes.

- 5. Reducción de la dimensiones (35%) y peso (40%) totales (de 1,1 kW/kg a 1,4 kW/kg y 2,6 kW/kg a 4 kW/kg, respectivamente).

A modo de ejemplo, el Departamento de Energía de EEUU tiene como objetivo lograr para 2020 desarrollar convertidores de potencia cuyas densidades de potencia sean superiores a 14,1 kW/kg y eficiencias superiores al 98 %. Estableciendo el precio objetivo de dichos convertidores por debajo de los 3,3 kW.

Teniendo en cuenta estos objetivos y desafíos, en las últimas décadas se han ido alcanzando gran cantidad de hitos tecnológicos, donde han predominado los desarrollos basados en semiconductores de potencia de silicio (Si). Los esfuerzos y desarrollos tanto de la industria de automoción, así como los requisitos y necesidades impuestss por diversos agentes políticos y sociales, están llevando el desarrollo de dicha tecnología hasta sus límites, lo que implica que las tecnologías actuales no pueden alcanzar estos nuevos desafíos.

En consecuencia, deben llevarse a cabo nuevas líneas de investigación, entre las cuales destacan el desarrollo y mejora de cada una de las partes fundamentales que constituyen el convertidor de potencia de los HEV/EV, tales como: sistemas avanzados de gestión térmica, nuevos diseños y componentes del DC-link, nuevas tecnologías de semiconductores de potencia, encapsulados optimizados, y topologías alternativas de conversión de potencia. En este contexto, el trabajo de investigación que se ha desarrollado en la presente tesis abarca los siguientes aspectos tecnológicos:

- □ Arquitecturas de la etapa de conversión de potencia. Las principales topologías que pueden ser implementadas en el tren de potencia para HEV/EV son descritas y analizadas, teniendo en cuenta las alternativas que mejor se adaptan a los requisitos técnicos que demandan este tipo de aplicaciones. De dicha exposición se identifican los elementos constituyentes fundamentales de los convertidores de potencia que forman parte del tren de tracción para automoción, siendo tomados estos elementos como el punto de partida para los distintos desarrollos y mejoras presentados a lo largo de la tesis.

- □ Nuevos dispositivos semiconductores de potencia. Los objetivos y retos tecnológicos anteriormente mencionados solo pueden lograrse median-

te el uso de nuevos materiales. Los semiconductores *Wide bandgap* (WBG), especialmente los dispositivos electrónicos de potencia basados en nitruro de galio (GaN) y carburo de silicio (SiC), son las alternativas más prometedoras al silicio (Si) debido a las mejores prestaciones que poseen dichos materiales, lo que permite mejorar la conductividad térmica, aumentar las frecuencias de conmutación y reducir las pérdidas. En este contexto, el conocimiento extraído de las alternativas comerciales proporciona una visión completa de las posibilidades de cada tecnología de semiconductores, así como su idoneidad para ser aplicadas.

□ Análisis de técnicas de rutado, conexionado y ensamblado de módulos de potencia. Los módulos de potencia fabricados con dies en lugar de dispositivos discretos son la opción preferida por los fabricantes para lograr las especificaciones indicadas por la industria de la automoción. Teniendo en cuenta los estrictos requisitos de eficiencia, fiabilidad y coste es necesario revisar y plantear nuevos *layouts* de las etapas de conversión de potencia, así como esquemas y técnicas de paralelización de los circuitos, centrándose en las tecnologías disponibles.

Teniendo en cuenta dichos aspectos, la primera parte de la investigación que se ha desarrollado evalúa las alternativas de tecnología de semiconductores de potencia que pueden ser implementadas en aplicaciones HEV/EV de acuerdo a sus requisitos. Este estudio del mercado de los semiconductores de potencia indica la existencia de dos tendencias, las tecnologías de silicio (Si) y los materiales WBG:

- □ El silicio (Si) representa la alternativa de mayor madurez y resultados contrastados, siendo el IGBT el semiconductor dominador del mercado de la electrónica de media potencia, nicho en el que se engloban las aplicaciones del tren de propulsión del sector de la automoción. Por dicha razón, se ha analizado en detalle las características, propiedades y la evolución de este dispositivo con el objetivo de obtener una visión de sus ventajas y desventajas. En este sentido, esta tecnología presenta dos principales desventajas, como son las relativas bajas frecuencias de conmutación, insuficientes para cumplir con los objetivos de pérdidas, y la baja conductividad térmica, donde se demandan materiales que puedan proporcionar mayores densidades de potencia ocupando menos espacio y peso.

- □ Los materiales WBG, entre los cuales destacan el carburo de silicio (SiC)y nitruro de galio (GaN) son los materiales con mayores posibilidades de ser empleados en el futuro en el sector de la automoción. A partir del estudio realizado se puede decir que, los dispositivos GaN presentan buenos comportamientos para altas frecuencias de conmutación, pero la estructura

lateral de los transistores, la conductividad térmica similar al Si, los bajos rangos de tensión/corriente, así como la falta de cierto grado de madurez y fiabilidad, hacen que su inmediata incorporación en el desarrollo de módulos de potencia no sea inmediata. A diferencia del GaN, los semiconductores basados en SiC muestran una perspectiva diferente, donde existe un nivel de desarrollo mucho más importante y una amplia variedad de dispositivos con múltiples rangos de operación. Estos factores hacen de esta tecnología, no solo por su estado actual de desarrollo, sino también por sus futuras perspectivas, una de las mejores opciones para cumplir los requisitos y retos que se ha citado anteriormente.

Una vez analizadas las alternativas de semiconductores de potencia, este trabajo estudia las conexiones internas del módulo de potencia para obtener los rangos de tensión y corriente necesarios para los vehículos eléctricos. En particular, para obtención de las densidades de potencia requeridas se ha empleado la técnica de paralelización de semiconductores de potencia. Previamente, para la correcta aplicación de dicha técnica de diseño ha sido necesario conocer las partes de los circuitos de conmutación implicadas, así como los principales elementos, destacando los siguientes:

- El comportamiento estático y dinámico de los semiconductores de potencia a paralelizar.

- El conexionado de la señales de control con los semiconductores de potencia.

- El circuito de potencia a través del cual fluyen las señales de alta corriente.

Tras identificar las ventajas y desventajas para llevar a cabo la paralelización de los semiconductores de potencia, queda patente la falta de referencias técnicas donde se indique de forma concreta y exhaustiva como realizar el diseño entre varios semiconductores de potencia evitando los posibles desequilibrios que se produzcan entre los dispositivos.

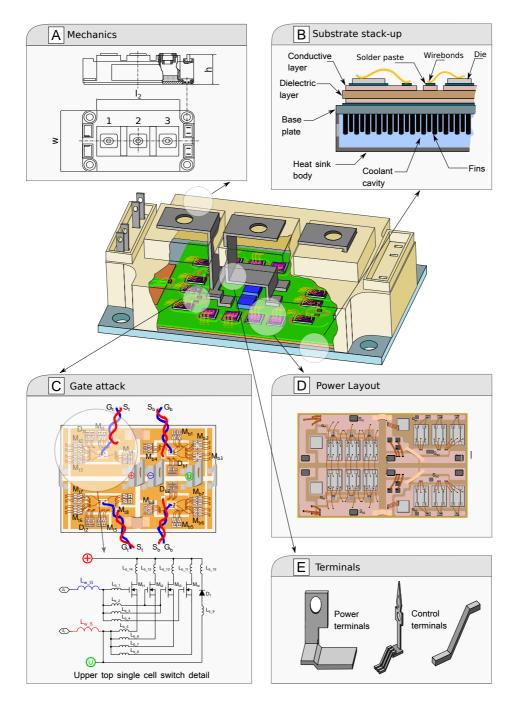

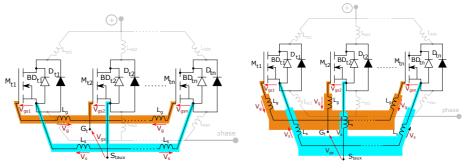

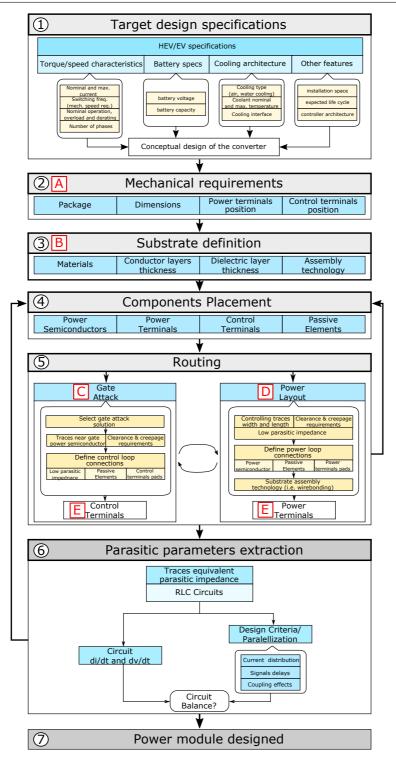

Debido a esta falta de información tanto científica como comercial e industrial, una de las principales contribuciones del presente trabajo ha sido la propuesta de una serie de criterios de diseño para el diseño de módulos de potencia, tomando como punto departida los módulos de potencia para aplicaciones HEV/EV. Dichos criterios parten de la recopilación de artículos científicos, así como de soluciones industriales/comerciales, donde se recogen soluciones locales para determinadas problemáticas, junto a otros documentos técnicos como datasheets y notas de aplicación. Toda esta información ha sido procesada para desarrollar y proponer los mencionados criterios de diseño, organizados y clasificados de acuerdo a un desglose del módulo de potencia en 5 partes fundamentales: mecánica, sustrato, ataque de compuerta, *layout* de potencia y terminales. En cada una de las mencionadas partes del módulo de potencia, han sido detalladas las estrategias para aplicar la simetría, así como otra serie de consejos para realizar un buen conexionado. Concretamente, en las partes de ataque de compuerta y *layout* de potencia se han presentado diversas soluciones para equilibrar las conexiones eléctricas entre los semiconductores de potencia para reducir las impedancias parásitas del circuito y diversos efectos adversos como acoplamientos entre las señales de control y potencia. Una vez desarrollados y extraídos los criterios de diseño para módulos de potencia, éstos han sido puestos en práctica para, así, validar las hipótesis propuestas. Para dicha validación se han utilizado diversas técnicas de simulación y co-simulación, tanto eléctrica como térmica, usando el *software* ADS<sup>TM</sup> y COMSOL Multiphysics, respectivamente.

Hay que tener en cuenta que un módulo de potencia es un diseño avanzado formado por múltiples partes, compactas entre sí, donde el espacio de diseño del *layout* es reducido, lo que dificulta el diseño de este tipo de soluciones. Por lo tanto, antes de cometer un desarrollo de tal índole, se ha recopilado información y experiencia a través del diseño de tres circuitos de potencia más simples. Estos circuitos son diversas partes de un convertidor de potencia, permitiendo comprender como aplicar la paralelización y la simetría en diferentes niveles de diseño. Dichos circuitos son un *switch* de potencia, un *half-bridge* y un *DC-link* implementados y diseñados sobre un sustrato PCB multicapa. El empleo de dicho sustrato ha facilitado el rutado de las pistas y áreas de cobre, ya que proporciona mayor flexibilidad al diseñador. Los resultados de simulación eléctrica que se han obtenido para cada uno de los circuitos muestran que las alternativas donde mejor han sido aplicadas las técnicas de paralelización y simetría garantizan el equilibrio de las corrientes en el circuito.

Comparado con otras soluciones como DBC/DBA y AMB, el uso de sustratos PCB aumenta claramente los valores de impedancia parásita. Esta es una de las razones por las que los circuitos de potencia para HEV/EV suelen implementarse sobre un formato de módulo de potencia. Por esta razón, esta tesis propone dos alternativas de módulo de potencia, utilizando la experiencia adquirida previamente en los circuitos diseñados sobre PCB. La topología de cada módulo es un *half-bridge*, donde se ha procurado reducir las longitudes de las conexiones eléctricas y equilibrar las conexiones entre los dispositivos en paralelo. Además, el sustrato empleado es una solución híbrida, una combinación de DBC y PCB, que permite aprovechar las ventajas de cada tecnología de sustrato. Así, por ejemplo, el rutado del ataque de compuerta se ha realizado de forma aislada respecto el *layout* de potencia, evitando los posibles efectos de retroalimentación.

Las dos propuestas de módulo de potencia *half-bridge* desarrolladas en esta tesis han sido las siguientes:

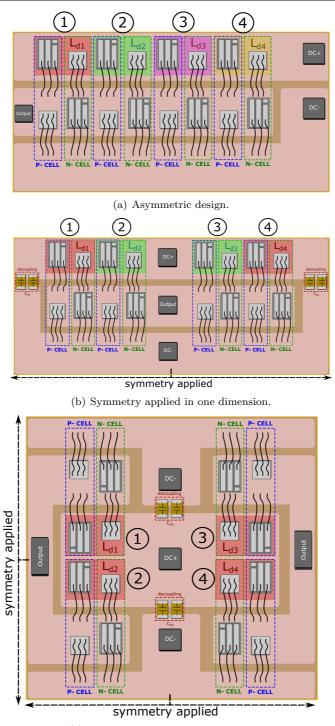

- Diseño symmetric: en este módulo de potencia se ha aplicado un concepto de simetría mucho más estricto que en el diseño cell. En el diseño symmetric, las conexiones son prácticamente idénticas, lo que repercute en el equilibrio de las corrientes que circulan por cada semiconductor de potencia.

- □ Diseño *cell*: en este módulo de potencia los principales beneficios se han debido a la implementación de las celda P y N (colocando lo mas próximo posibles el MOSFET y el diodo que forman el lazo de conmutación) con condensadores (*snubbers*) entre los MOSFETs y diodos, permitiendo reducir los caminos de conmutación y equilibrar los diversos lazos cerrados del circuito.

De acuerdo a los resultados obtenidos en las simulaciones eléctricas, ambas soluciones no muestran retardos críticos en las señales de control que puedan producir desequilibrios de corriente, poniendo en peligro la integridad del sistema. Además, la aplicación de las técnicas de paralelización y simetría permiten diseñar conexionados entre los semiconductores de potencia con impedancias parásitas similares, igualando las corrientes que circulan por cada dispositivo.

Además del estudio eléctrico se ha realizado también un estudio térmico para cada una de las soluciones de módulo de potencia propuestas, concretamente se han realizado simulaciones electro-térmicas de los *layout* de potencia de cada uno de las soluciones. En dichas simulaciones se ha propuesto una metodología que combina simulaciones 1D y 3D para poder aplicar perfiles de conducción de vehículo eléctrico y así someter los diseños a situaciones reales. Los resultados obtenidos para ambos módulos de potencia propuestos no han mostrado puntos críticos que indiquen un comportamiento de los circuitos por encima de las temperaturas de operación de los semiconductores que producirían la ruptura de los mismos.

Finalmente, los resultados que se han extraído de los circuitos propuestos demuestran la utilidad de los criterios de diseño propuestos, obteniendo circuitos de potencia con bajas impedancias parásitas, equilibrados eléctrica y térmicamente. A nivel industrial, el conocimiento expuesto en la presente tesis permite reducir los tiempos de diseño a la hora de obtener prototipos de ciertas garantías, ya que los criterios de diseño expuestos permiten comenzar la fase de prototipado habiéndose realizado muchas comprobaciones eléctricas y térmicas.

#### Laburpena

Faktore asko dira gaur egungo ibilgailuen teknologien elektrifikazio partziala edo osoa lortzeko interesa areagotu dutenak, hala nola gero eta zorrotzagoak diren gas kutsatzaileen emisio-politikak, erregai fosilen urritasuna eta hauen prezioen hegazkortasuna. Halaere, barne errekuntzako motoreetan oinarritutako ibilgailuetatik abiatuta motore elektrikotan oinarritutako etarako trantsizioa era mailakatuan ematen ari da. Hainbat mugarri teknologiko lortu dira azkenengo harmakadetan, oinarrizko osagaien garapenetik hasi eta silizioan (Si) egindako potentzia moduluekin eginiko eragingailu elektriko integratuetaraino. Testuinguru honetan, ibilgailuen industriak zein eragile politikoek eta sozialek gaur egungo eragingailu elektrikoen teknologia bere muturretara bultzatzen ari dira. Hala nola DOE, Horizon 2020, USCAR eta UN ESCAP bezalako erakundeek potentzia eletronikoari dagozkion hurrengo helburu teknologikoak ezarri dituzte:

- 1. Bihurgailuaren potentzia-dentsitatearen % 50-eko igoera (8,7 kW/l-tik 13,4 kW/l-ra).

- 2. Bihurgailuaren eroate eta kommutazio-galeren % 50-eko murrizketa.

- 3. Potentzia-elektronikaren fabrikazio kostua murriztea (30 $k/kW-tik \$  %/kW-ra).

- 4. Hozte-prozesuaren sinplifikazioa eta osagaien murrizketa.

- 5. Masa (% 35) eta bolumen (% 40) totalaren murrizketa, 1,1 kW/kg-tik 1,4 kW/kg-ra eta 2,6 kW/l-tik 4 kW/l-ra.

Esate baterako, AEB<br/>ko energia-sailak%14.1 kW/kg-ko potentzia-dentsi<br/>tatea eta%98-ko eraginkortasuna duten potentzia-bihurgailuen garapena espero du 2020 urterako, hau den<br/>a3,3\$/kW-tako preziotik behera.

Helburu hauek trakzio-sistemaren atal nagusien garapena sustatzen dute. Bateria, potentzia-bihurgailua eta motorea. Lan honen ikerketa-ildoa aipatutako helburuak burutzeko beharrezkoak diren potentzia-moduluen azterketara eta garapenera bideratzen da.

Ildo honetan, lan honek potentziako-erdieroaleen artearen egoera sakon bat eta moduluen barne diseinuko aspektu asko aurkezten ditu. Beraien goi-mailako ezaugarriak direla eta, banda zabaleko erdieroaleak (*Wide bandgap, WBG*), silizio karburoan (*SiC*) oinarritutakoak batez ere, siliziozko erdieroaleen etorkizuneko aukera bezala aurkezten dira. Honekin batera, gaur egungo silizio eta WBG teknologiaren merkatu azterketa bat egin eta potentzia-modulu baten barruan muntatzeko gailu egokienak azpimarratzen dira.

Potentziako-erdieroaleen teknologiaz gain, paralelizatutako gailuen konexio elektrikorako kontzeptu garrantzitsuenak aztertu dira. Kontzeptu hauek potetnzia-moduluen diseinurako irizpideak proposatzeko eta garatzeko erabiliko dira, eginkizun hau erraztuz. Potentzia-moduluen eskakisun elektrikoak kontuan hartuta, potentzia-moduluen diseinurako irizpideen kontzeptu garrantzitsuenak identifikatu dira literatura zientifikoa, industriala eta komertziala aztertuz horretarako. Irizpide hauek, WBG die-ak era optimoan paralelizatzeko kontrol eta potentzia seinaleak modu egokian bideratzea ahalbidetzen dute.

Aurkeztutako diseinu-irizpide hauek PCB sustratoan oinarritutako hiru zirkuituetan baieztatu dira, hauen jokaera ikertzeko simulazio elektrikoak erabiliz (zirkuituen eredu elektromagnetikoa + potentzia-erdieroaleen Spice-eko eredua). Zirkuitu hauetan paralelizazio eta simetria-kontzeptuak modu mailakatu batean erabili dira, hauek potentzia bihurgailu baten hiru atal ezberdin irudikatuz: potentzia-etengailua, half-bridge-a eta DC-link-a. Emaitzak, bi kontzeptu hauen mailakatze eta korronte-tentsio oreken arabera sailkatu eta aurkeztu dira.

Azkenik, bi potentzia-modulu proposamen aurkeztu dira: symmetric eta cell diseinuak. Biak half-bridge topologiak dira (potentzia-bihurgailuen oinarrizko osagaia kontsideratuta), eta bietan erabili dira tesian garatutako diseinu irizpide nagusiak. Symmetric diseinuan simetria-kontzeptu zorrotzago bat erabiliz erdieroale bakoitzean korronte oraken eragin da. Cell diseinuko abantaila nagusiak erdieroaleen kokapenagatik ematen dira, snubber kondentsadoredun P eta N cell konfigurazioak ezarri dira (MOSFET-ak eta diodoak konmutazio bukletik ahal dan gertuenen kokatzen dira) konexioen luzapena txikiagotuz eta zirkuitua orekatuz. ADS<sup>TM</sup>-ko simulazioak aplikatutako diseinu-irizpideak balioztatzeko erabili dira. Honekin batera, 1D eta 3D simulazio-teknikak, Matlab eta COMSOL Multiphysics konbinatzen duten metodologia espezifiko bat garatu da modelo elektro-termiko konplexu bat lortzeko. Aipatutako guztia potentzia-moduluak egoera errealetako baldintzetan testeatzeko erabili da, puntu kritikoak eta fidagarritasun arazoak ez daudela baieztatuz.

xvii

Simulazio hauek, EV/HEV-tarako proposatutako potentzia-moduluen diseinuirizpideak egiaztatzeko balio izan dute. Metodologia honen bitartez diseinuko arazo asko ekiditu ahal daitezkenez, prototipaziorako pausoa aurreratu, prototipazioa puntu tekniko hobe batetik hasi eta garapenaren denbora osoa murrizten da.

## Contents

| $\mathbf{A}$ | bstra | act   Resumen   Laburpena                                        | v         |

|--------------|-------|------------------------------------------------------------------|-----------|

| Li           | st of | Figures                                                          | cxiii     |

| Li           | st of | Tables                                                           | xxix      |

| Li           | st of | Acronyms                                                         | xxxi      |

| Li           | st of | Symbols x                                                        | xxv       |

| 1            | Intr  | roduction                                                        | 1         |

|              | 1.1   | Thesis context                                                   | 1         |

|              | 1.2   | Introduction to the research topics                              | 3         |

|              | 1.3   | Power electronics in HEV/EV applications                         |           |

|              |       | 1.3.1 Battery and power semiconductors: electric operation con-  |           |

|              |       | ditions                                                          | 8         |

|              |       | 1.3.2 Power conversion topology                                  |           |

|              |       | 1.3.3 Influence of future electric machine design considerations | 0         |

|              |       | on power electronics                                             | 13        |

|              |       | 1.3.4 Thermal management constraints                             |           |

|              |       | 1.3.5 Electromagnetic interference constraints                   |           |

|              | 1.4   | Objectives                                                       |           |

|              | 1.5   | Document structure                                               |           |

| <b>2</b>     | Sili  | icon $(Si)$ power semiconductor technology                       | <b>23</b> |

|              | 2.1   | Introduction                                                     | 23        |

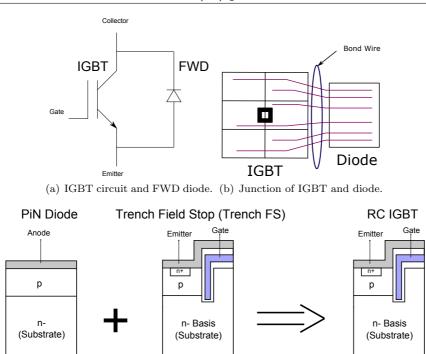

|              | 2.2   | IGBT technology and evolution                                    | -         |

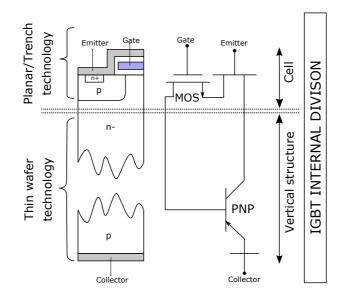

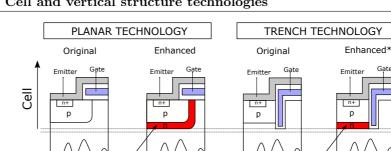

|              | 2.3   | Cell and vertical structure technologies                         |           |

|              |       | 2.3.1 IGBT cell: planar and <i>trench</i> technologies           |           |

|              |       | 2.3.2 IGBT vertical structures: thin wafer technology            |           |

|   | 2.4  |                                                              | 34         |

|---|------|--------------------------------------------------------------|------------|

|   | 2.5  |                                                              | 36         |

|   | 2.6  | 1 00                                                         | 37         |

|   | 2.7  | 1 00                                                         | 39         |

|   | 2.8  |                                                              | 40         |

|   | 2.9  |                                                              | 12         |

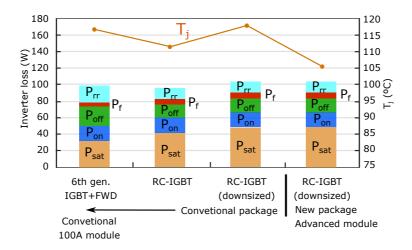

|   | 2.10 | IGBT with antiparallel diode: RC IGBT 4                      | 13         |

|   | 2.11 | Conclusions                                                  | 16         |

| 3 | Wid  | le bandgap (WBG) technology 4                                | 19         |

|   | 3.1  |                                                              | 19         |

|   | 3.2  |                                                              | 53         |

|   |      |                                                              | 33         |

|   |      | 3.2.2 SiC BJT                                                | 35         |

|   |      | 3.2.3 <i>SiC</i> JFET                                        | 66         |

|   |      | 3.2.4 <i>SiC</i> MOSFET                                      | 37         |

|   |      | 3.2.5 $SiC$ IGBT                                             | 70         |

|   | 3.3  | Gallium Nitride (GaN) devices                                | 71         |

|   |      | 3.3.1 $GaN$ diodes                                           | 73         |

|   |      | 3.3.2 $GaN$ transistors                                      | 73         |

|   | 3.4  | Conclusions                                                  | 76         |

| 4 | Para | allelization of power semiconductors 7                       | <b>'</b> 9 |

|   | 4.1  | Introduction                                                 | 79         |

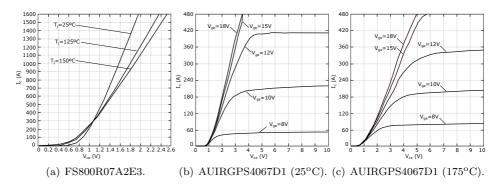

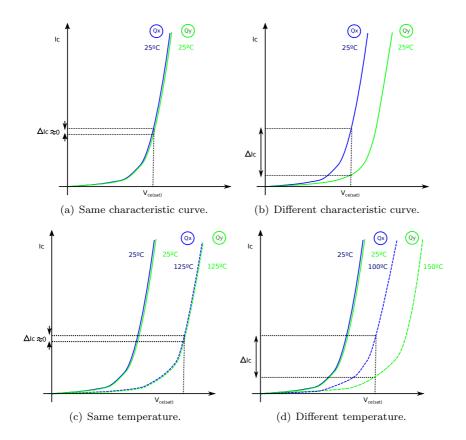

|   | 4.2  | Power semiconductor static behaviour                         | 31         |

|   |      | 4.2.1 Temperature dependency on the semiconductor electrical |            |

|   |      | parameters                                                   | 31         |

|   |      |                                                              | 34         |

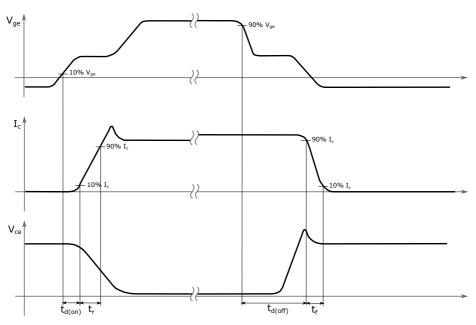

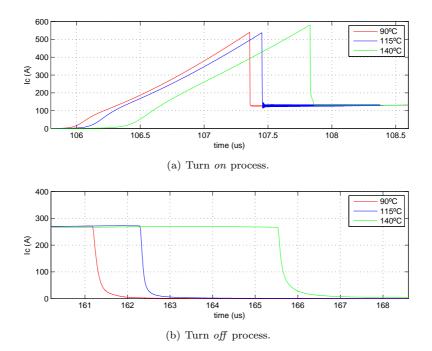

|   | 4.3  | Power semiconductor dynamic behaviour                        | 36         |

|   |      | 1 1 0                                                        | 37         |

|   |      | 0 0                                                          | 39         |

|   | 4.4  |                                                              | 90         |

|   |      | 0 1                                                          | 91         |

|   |      |                                                              | 95         |

|   | 4.5  | v                                                            | 96         |

|   |      |                                                              | 96         |

|   |      | ( 01)                                                        | 99         |

|   | 4.6  | Conclusions                                                  | )2         |

| 5 | Ana  | lysis and definition of the power module design criteria 10  | )3         |

| - | 5.1  | Introduction                                                 |            |

|   | 5.2            | Power    | module mechanics                                                                                                                              | . 105 |

|---|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|

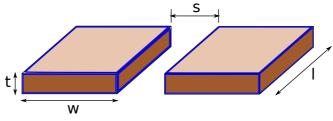

|   | 5.3            | Substr   | ate stack-up: thermal behaviour                                                                                                               | 108   |

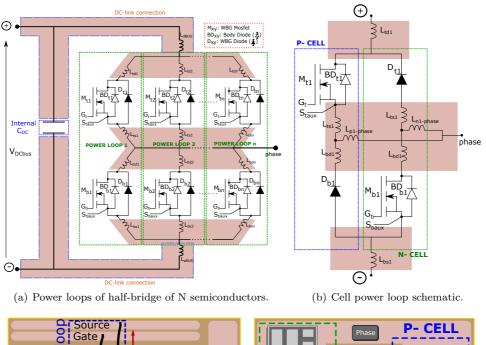

|   | 5.4            | Gate a   | ttack: control signals                                                                                                                        | . 110 |

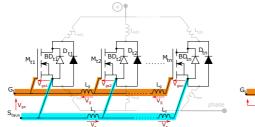

|   | 5.5            | Power    | layout: power signals                                                                                                                         | . 116 |

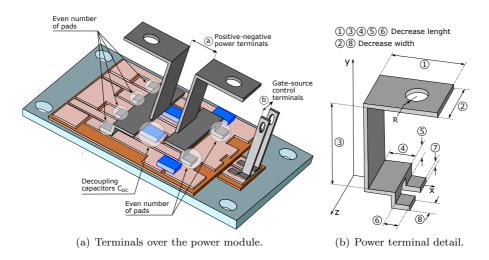

|   | 5.6            | Termin   | nals: power and control                                                                                                                       | . 121 |

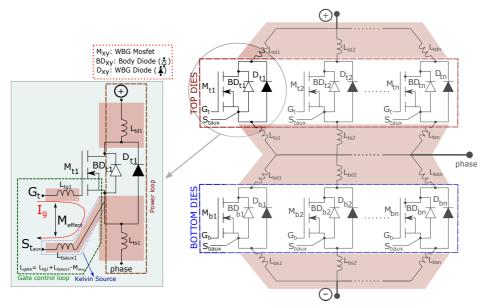

|   | 5.7            |          | steps of the $SiC$ power module $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                            |       |

|   | 5.8            | Conclu   | sions                                                                                                                                         | . 123 |

| 6 | Para           | alleliza | tion of power converter circuits (PCC) according to                                                                                           | D     |

|   | $\mathbf{the}$ |          | sed design criteria                                                                                                                           | 129   |

|   | 6.1            | Introd   | $uction \ldots \ldots$ | . 129 |

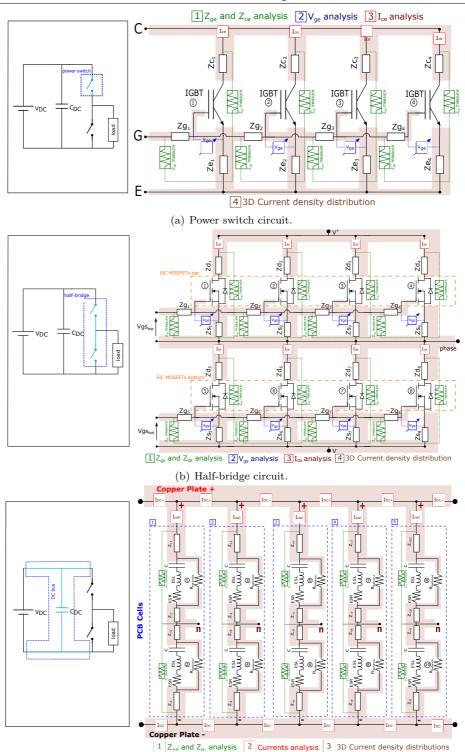

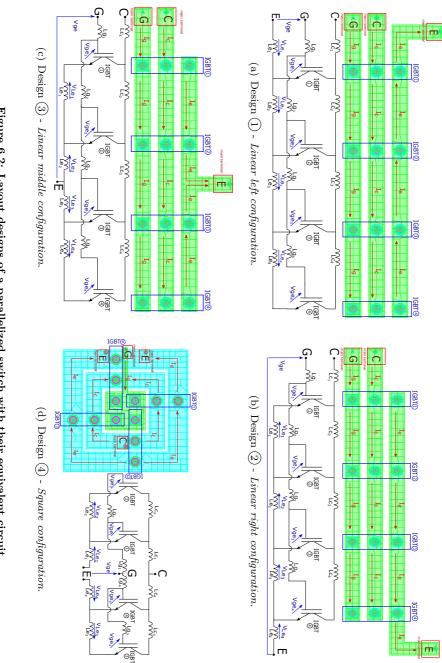

|   | 6.2            | Power    | switch based on semiconductor parallelization $\ldots \ldots \ldots$                                                                          | . 130 |

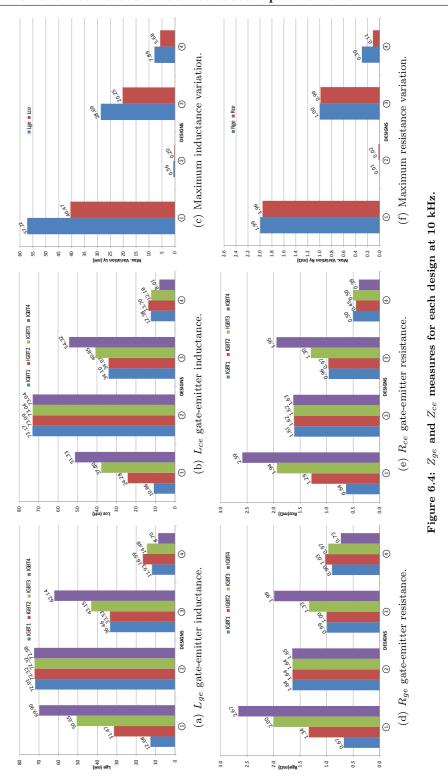

|   |                | 6.2.1    | Closed loop impedances: gate-emitter and collector-emitter                                                                                    | 133   |

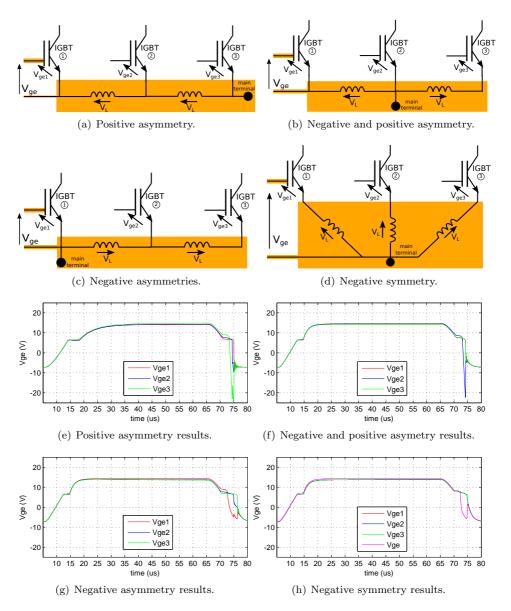

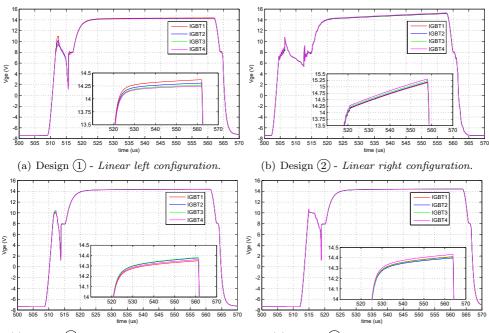

|   |                | 6.2.2    | Gate-emitter closed loop influence on $V_{ge}$ signals $\ldots$ $\ldots$                                                                      | . 134 |

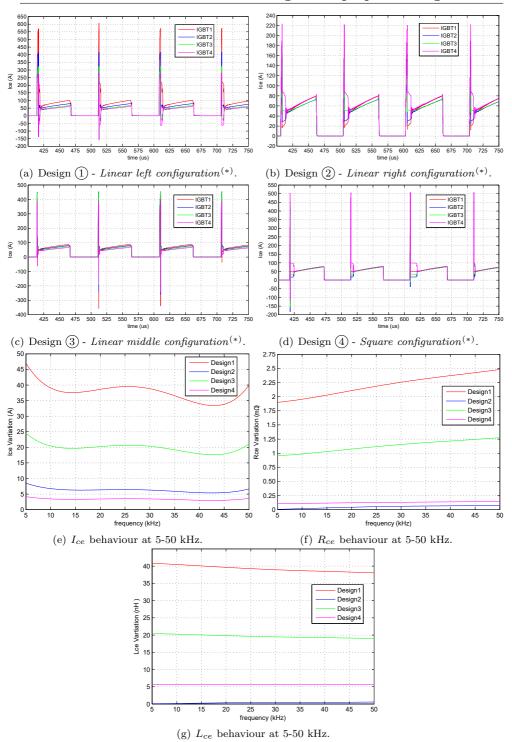

|   |                | 6.2.3    | Collector-emitter closed loop influence on $I_{ce}$                                                                                           | . 137 |

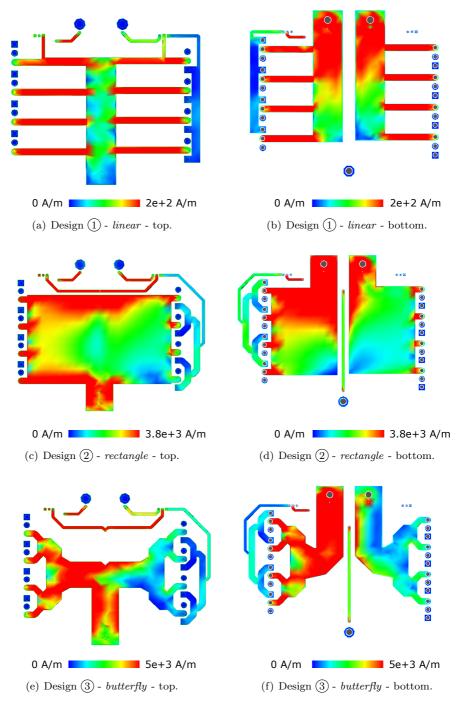

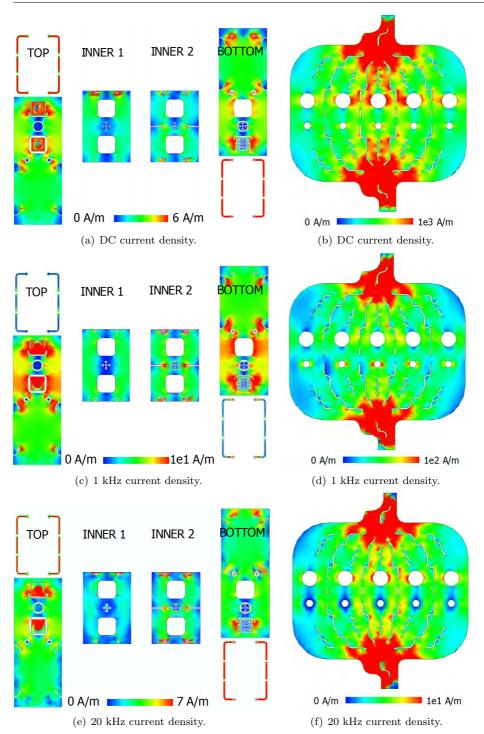

|   |                | 6.2.4    | Current density distribution over the power switches                                                                                          | 139   |

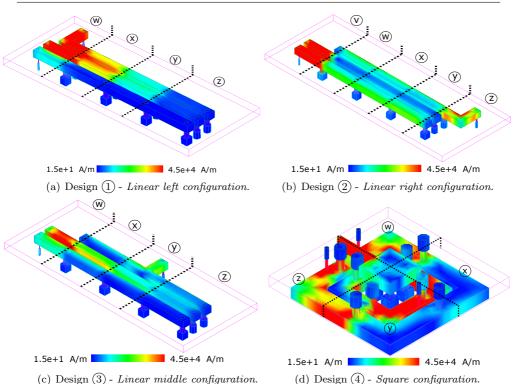

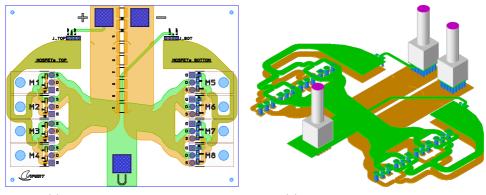

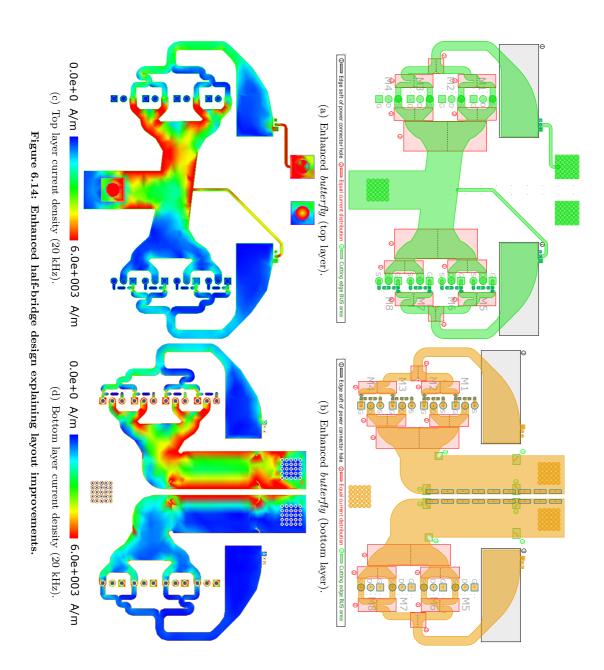

|   | 6.3            | Half-b   | ridge based on the layout symmetry $\ldots \ldots \ldots \ldots \ldots$                                                                       |       |

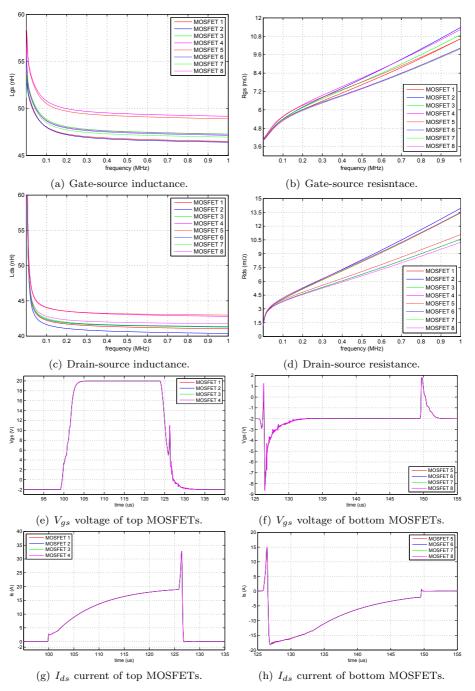

|   |                | 6.3.1    | Closed loop impedances: gate-source and collector-source .                                                                                    |       |

|   |                | 6.3.2    | Gate-source closed loop influence on $V_{gs}$                                                                                                 |       |

|   |                | 6.3.3    | Collector-source closed loop influence on $I_{ds}$                                                                                            |       |

|   |                | 6.3.4    | Half-bridge current density distributions                                                                                                     |       |

|   |                | 6.3.5    | Techniques to Round tracks and cutting edges                                                                                                  |       |

|   | 6.4            |          | ayer DC bus design                                                                                                                            |       |

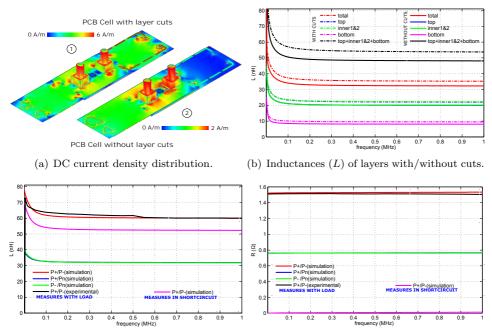

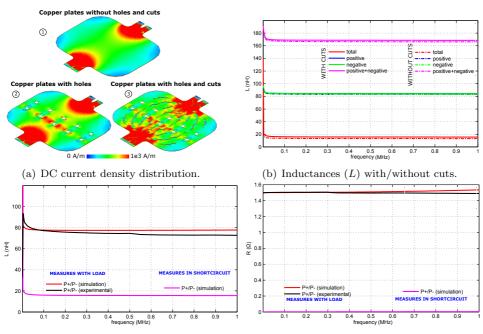

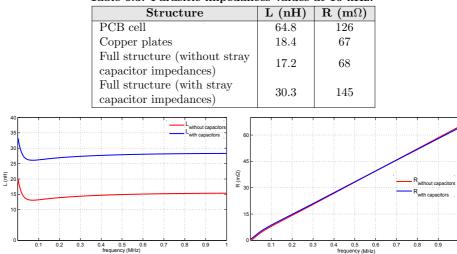

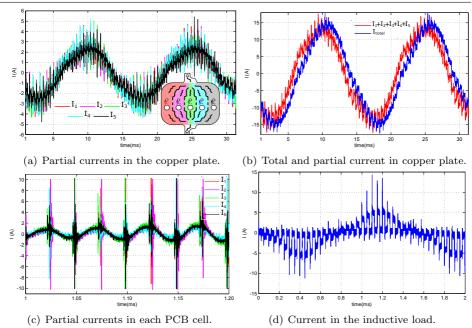

|   |                | 6.4.1    | Power multilayer PCB: stray inductance study                                                                                                  |       |

|   |                | 6.4.2    | Copper plates: stray inductance study                                                                                                         |       |

|   |                | 6.4.3    | DC bus assembly                                                                                                                               |       |

|   |                | 6.4.4    | Current balance and current density distribution                                                                                              |       |

|   | 6.5            | Conclu   | nsions                                                                                                                                        | . 164 |

| 7 |                |          | ridge module development based on the proposed de                                                                                             |       |

|   | 0              | criter   |                                                                                                                                               | 165   |

|   | 7.1            |          | $uction \ldots \ldots$ | 165   |

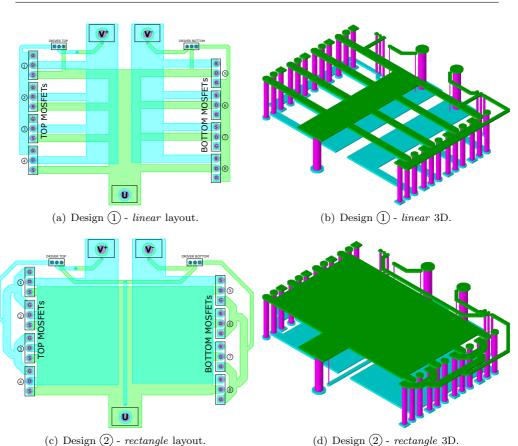

|   | 7.2            |          | cal characterization: layouts according to the proposed de-                                                                                   |       |

|   |                | 0        | iteria                                                                                                                                        |       |

|   |                | 7.2.1    | Power module mechanics                                                                                                                        |       |

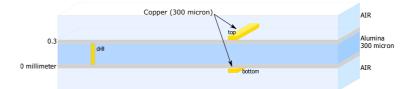

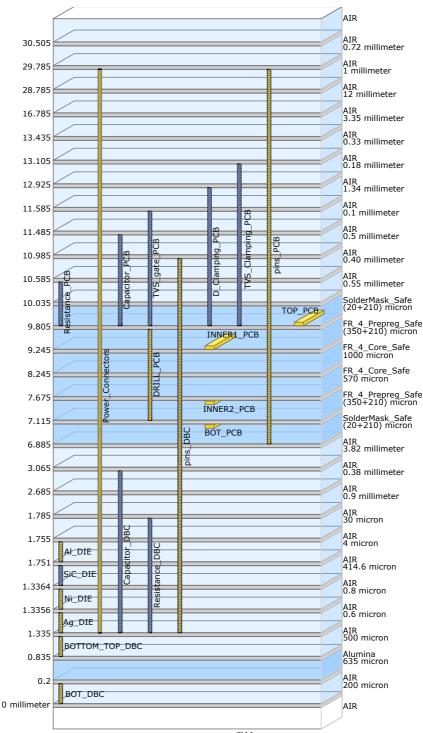

|   |                | 7.2.2    | Substrate stack-up: vertical hybrid configuration                                                                                             |       |

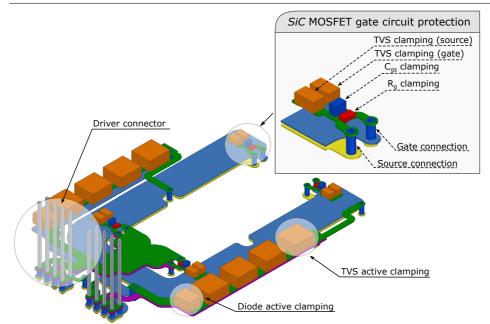

|   |                | 7.2.3    | Gate attack: embedded PCBs                                                                                                                    |       |

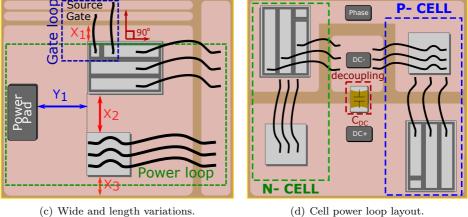

|   |                | 7.2.4    | Power layout: Direct Bonding Copper (DBC)                                                                                                     |       |

|   | _              | 7.2.5    | Terminals: DC bus and phase/output connectors                                                                                                 |       |

|   | 7.3            |          | al characterization: vertical substrate design                                                                                                |       |

|   |                | 7.3.1    | Definition of the power layout and initial approximation                                                                                      | . 198 |

|              |                | 7.3.2 Determination of the equivalent Foster networks           | 201        |

|--------------|----------------|-----------------------------------------------------------------|------------|

|              |                | 7.3.3 Determination of power dissipation profiles by means of   | 004        |

|              |                | real-time simulation                                            | 204        |

|              |                | 7.3.4 3D temperature characterization of the power modules over | 005        |

|              | <b>H</b> 4     | the entire driving cycle                                        |            |

|              | 7.4            | Conclusions                                                     | 205        |

| 8            | Con            | clusions and future work                                        | <b>211</b> |

|              | 8.1            | Conclusions                                                     | 211        |

|              | 8.2            | Main contributions                                              | 215        |

|              | 8.3            | Scientific publications in the context of this work             | 218        |

|              | 8.4            | Future work                                                     | 221        |

|              | 8.5            | Acknowledgements                                                | 223        |

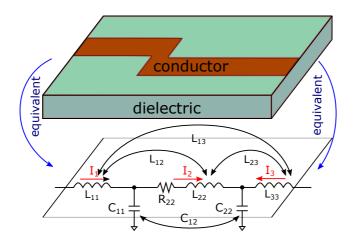

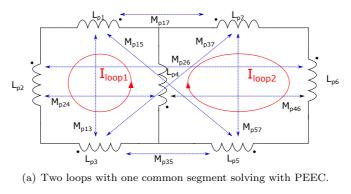

| $\mathbf{A}$ | $\mathbf{Ext}$ | raction of parasitic elements from the designed power elec      | _          |

|              | tror           | nic modules                                                     | <b>225</b> |

|              | A.1            | Partial Element Equivalent Circuit (PEEC)                       | 226        |

|              | A.2            | Mesh model development for non ideal circuit simulations        | 228        |

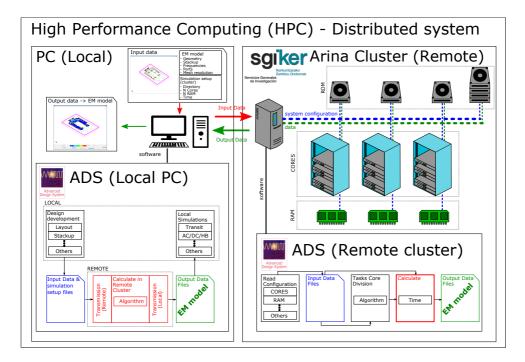

|              |                | Arina (SGIker)                                                  |            |

|              |                | A.3.1 Infrastructure                                            | 229        |

|              |                | A.3.2 Data processing center                                    |            |

| в            | The            | rmal 1D and 3D simulations for driving cycle profiles           | 233        |

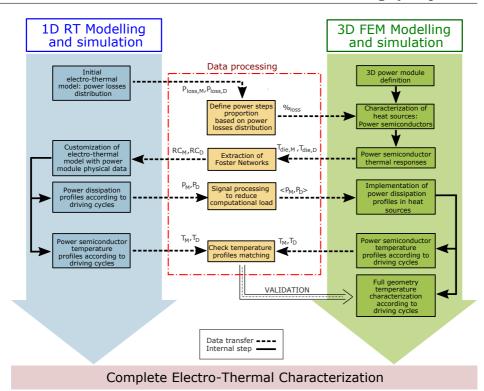

|              | B.1            | Proposed hybrid 1D/3D electro-thermal procedure                 | 235        |

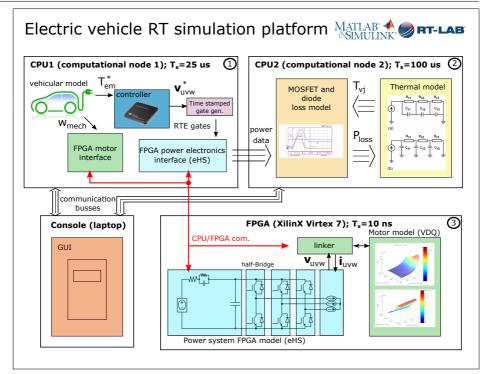

|              | B.2            | Real-time 1D electro-thermal simulation platform                |            |

|              | B.3            | -                                                               |            |

| R            |                |                                                                 |            |

\_\_\_\_\_

# List of Figures

| 1.1  | Worldwide EV and PHEV sales forecasted by the BLUE Map sce-                |     |

|------|----------------------------------------------------------------------------|-----|

|      | nario (in millions per year)                                               | 5   |

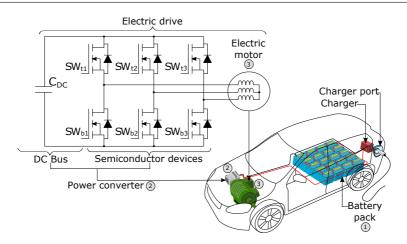

| 1.2  | Explosion drawing of an automotive electric drive system main              |     |

|      | components                                                                 | 6   |

| 1.3  | Generic power converter topology of future HEV/EV electric                 |     |

|      | drives based on two-level multiphase topologies and with paral-            |     |

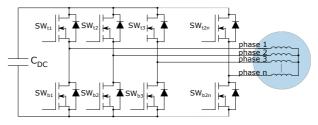

|      | lelized power switches.                                                    | 9   |

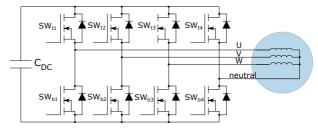

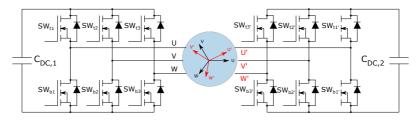

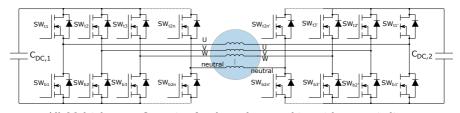

| 1.4  | Alternative fault tolerant multiphase power conversion topologies          |     |

|      | for HEV/EV drives.                                                         | 11  |

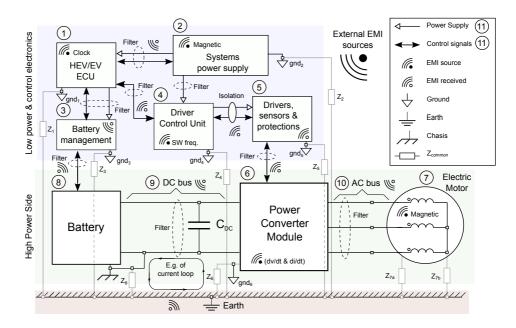

| 1.5  | Identification of EMI sources in HEV/EV applications                       | 17  |

| 0.1  |                                                                            | 0.4 |

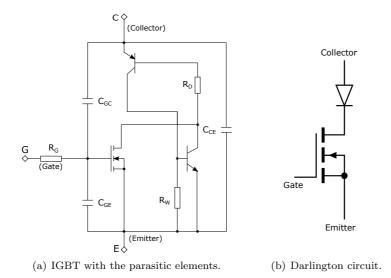

| 2.1  | IGBT equivalent circuit representations                                    | 24  |

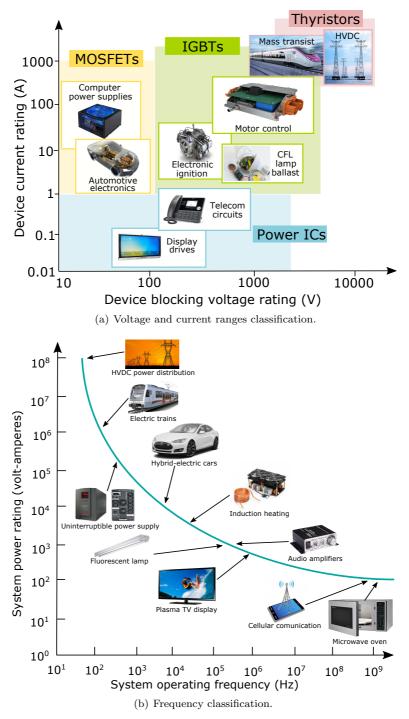

| 2.2  | Power electronics applications.                                            | 25  |

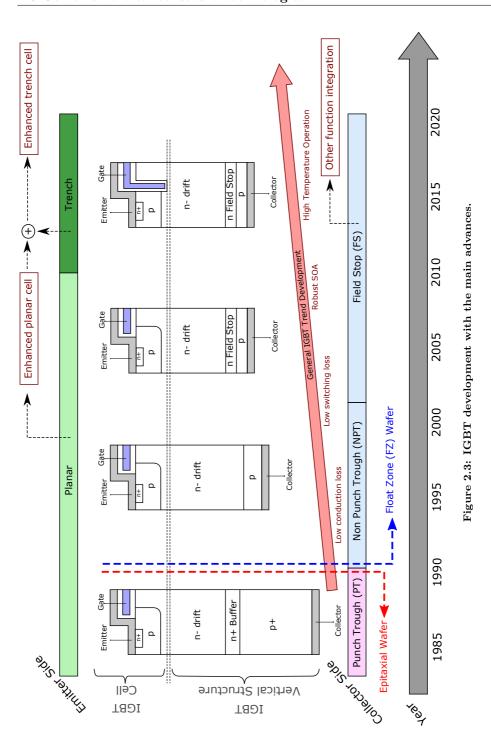

| 2.3  | IGBT development with the main advances                                    | 27  |

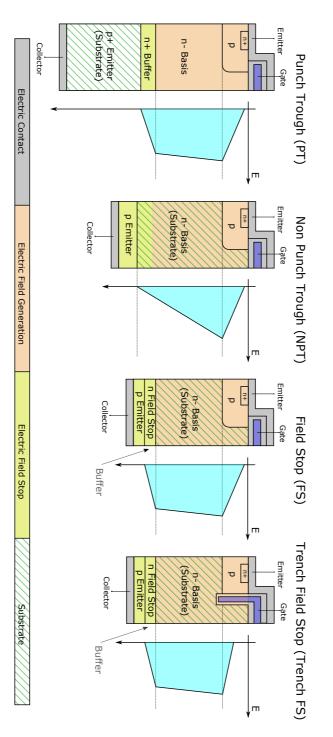

| 2.4  | Main IGBTs topologies with their electric fields and layer structures.     | 28  |

| 2.5  | Enhanced IGBT structures.                                                  | 29  |

| 2.6  | IGBT internal structure and Darlington equivalent circuit                  | 30  |

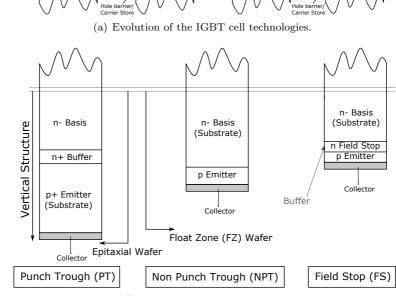

| 2.7  | Cell and vertical structures technologies.                                 | 31  |

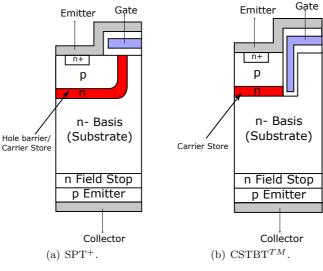

| 2.8  | Improvement of planar cells with hole barrier/carrier store layer.         | 32  |

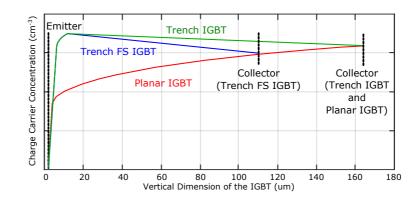

| 2.9  | Comparative of the carrier concentration for the IGBT topologies.          | 33  |

| 2.10 | Conduction and turn off behaviour of trench IGBTs according to             |     |

|      | trench cell width                                                          | 33  |

| 2.11 | Behaviour at different temperatures of the voltage $V_{ce_{sat}}$ over the |     |

|      | current $I_c$ for the PT and NPT IGBTs                                     | 35  |

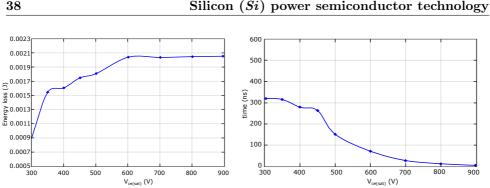

|      | FS IGBT behaviour.                                                         | 38  |

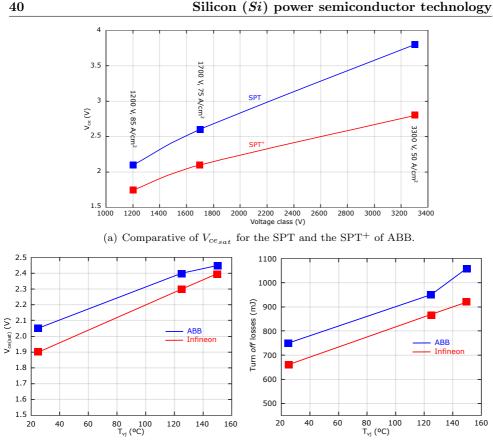

|      | $SPT^+$ technology behaviour                                               | 40  |

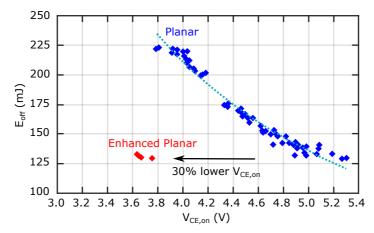

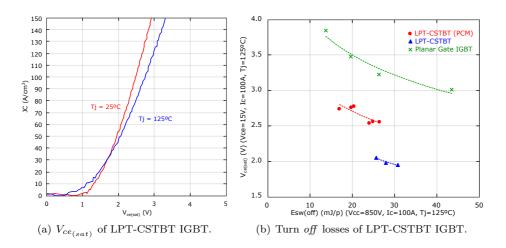

|      | Comparative of CSTBT IGBTs with planar PT IGBTs                            | 42  |

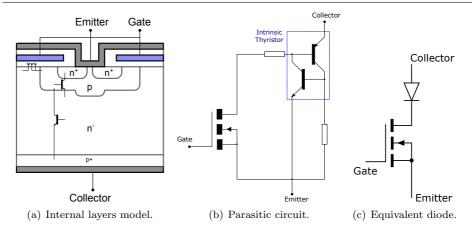

|      | IGBT intrinsic diode                                                       | 43  |

| 2.16 | RC IGBT structure and external FWD diode                                   | 44  |

| 2.17 | Losses of the RC IGBT and the IGBT + FWD assembly of an inverter.                           | 46 |

|------|---------------------------------------------------------------------------------------------|----|

|      |                                                                                             | 10 |

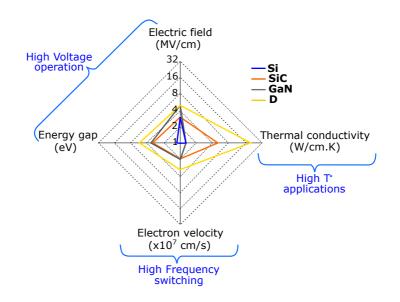

| 3.1  | Market trend in WBG technology.                                                             | 50 |

| 3.2  | Current status of potential wide bandgap materials                                          | 51 |

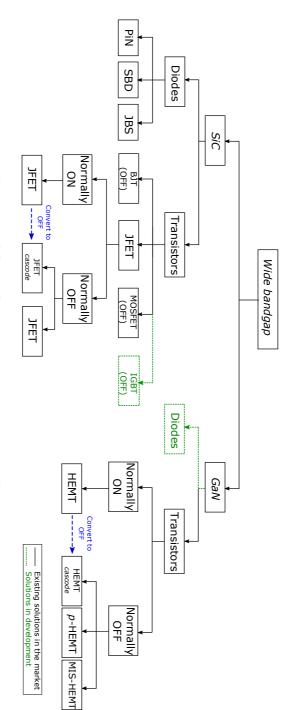

| 3.3  | SiC and $GaN$ power semiconductors classification                                           | 52 |

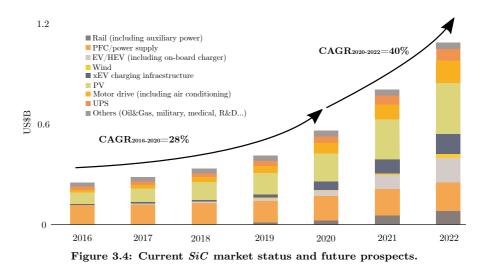

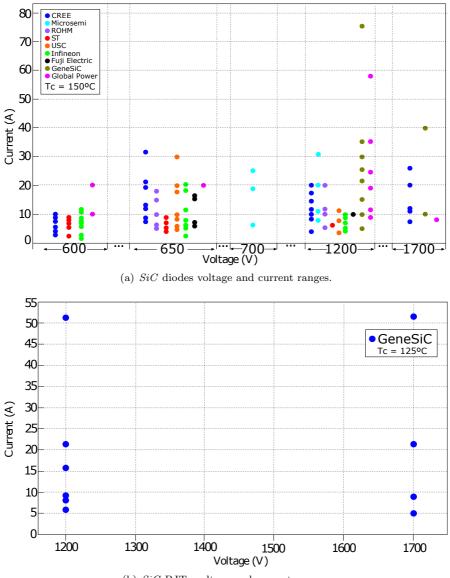

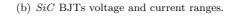

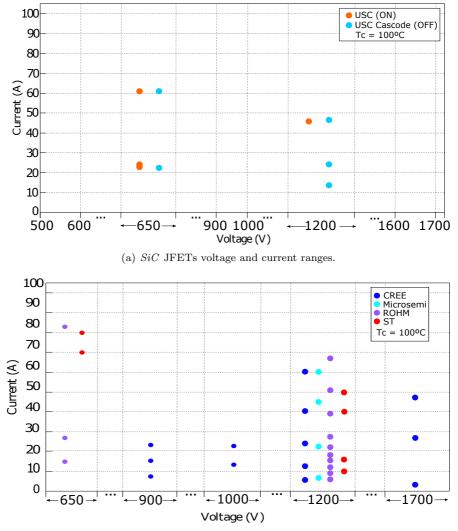

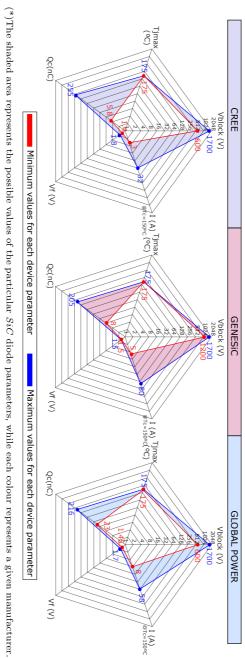

| 3.4  | Current $SiC$ market status and future prospects                                            | 53 |

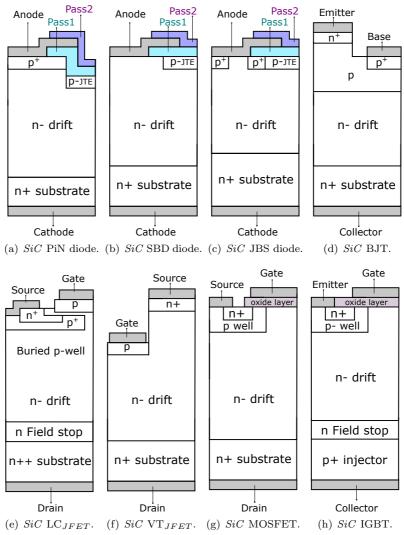

| 3.5  | Internal structure of $SiC$ devices                                                         | 55 |

| 3.6  | Voltage and current ratings of $SiC$ devices available on the market                        |    |

|      | (I)                                                                                         | 56 |

| 3.7  | Voltage and current ratings of $SiC$ devices available on the market                        |    |

|      | (II)                                                                                        | 57 |

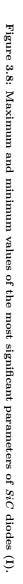

| 3.8  | Maximum and minimum values of the most significant parameters                               |    |

|      | of $SiC$ diodes (I)                                                                         | 58 |

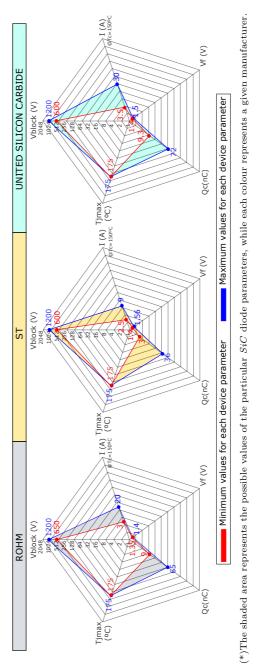

| 3.9  | Maximum and minimum values of the most significant parameters $f(G) = G(G)$                 | 50 |

| 0.40 | of $SiC$ diodes (II)                                                                        | 59 |

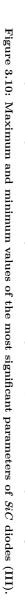

| 3.10 | Maximum and minimum values of the most significant parameters $f(G,G, H) = h_{G}(G, H)$     | co |

| 0.11 | of $SiC$ diodes (III)                                                                       | 60 |

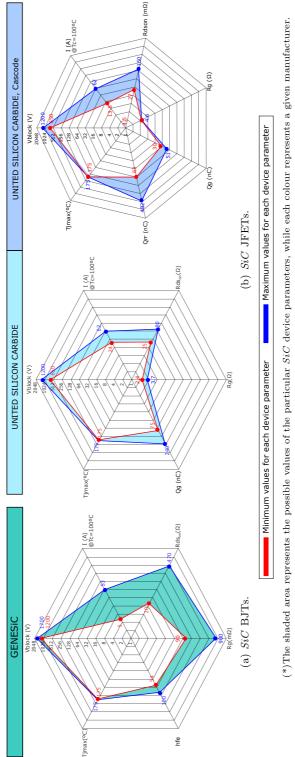

| 3.11 | Maximum and minimum values of the most significant parameters of <i>SiC</i> BJTs and JFETs. | 61 |

| 3 19 | Maximum and minimum values of the most significant parameters                               | 01 |

| 0.12 | of SiC MOSFETs.                                                                             | 62 |

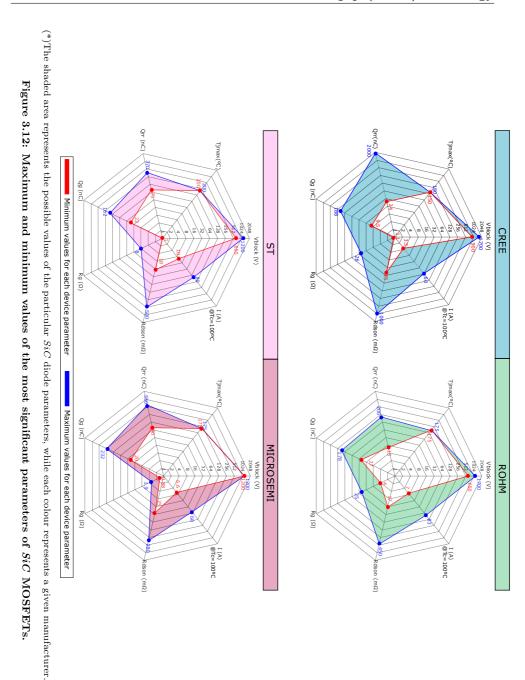

| 3.13 | Charge comparative of $Si$ and $SiC$ diodes                                                 | 64 |

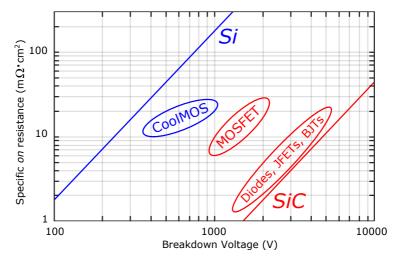

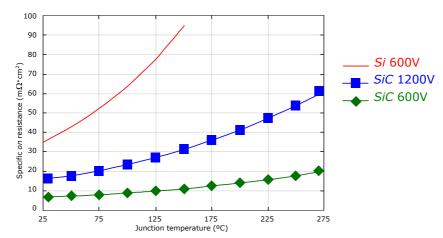

|      | Breakdown voltages and <i>on</i> resistance of <i>SiC</i> devices.                          | 65 |

|      | Variation of $on$ resistance with the temperature over $SiC$ JFET                           |    |

| 0.20 | devices and $Si$ technology                                                                 | 66 |

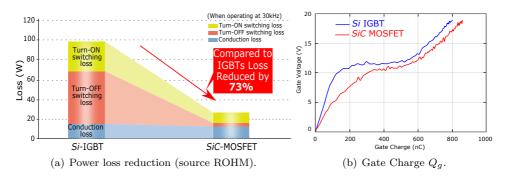

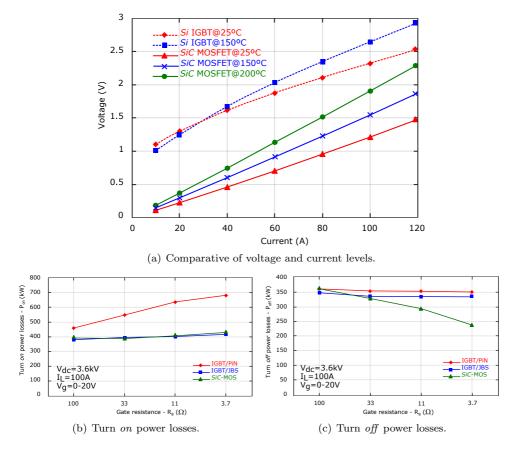

| 3.16 | Comparation of SiC MOSFET and Si IGBT                                                       | 67 |

|      | Comparative of <i>SiC</i> MOSFET and <i>Si</i> IGBT                                         | 68 |

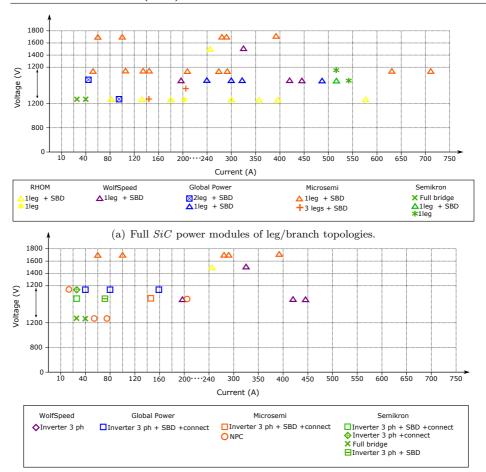

| 3.18 | Commercial full $SiC$ power modules                                                         | 69 |

|      | Comparison of <i>freewheeling</i> diodes with Si IGBT respect to gate                       |    |

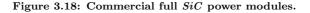

|      | resistance $(R_g)$ .                                                                        | 70 |

| 3.20 | Comparison of breakdown voltage and on resistance for semicon-                              |    |

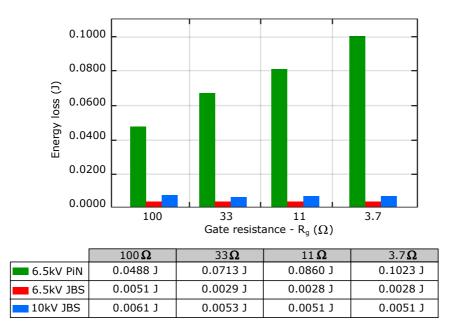

|      | ductor material alternatives                                                                | 71 |

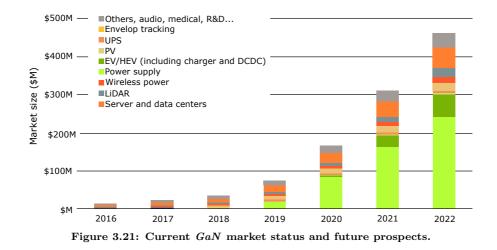

|      | Current $GaN$ market status and future prospects                                            | 72 |

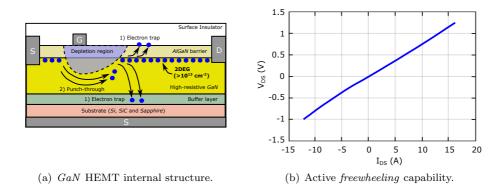

|      | GaN HEMT transistor.                                                                        | 74 |

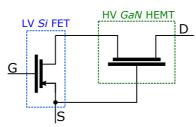

| 3.23 | Cascode configuration of GaN HEMT transistor to get normally                                |    |

|      | off operation                                                                               | 74 |

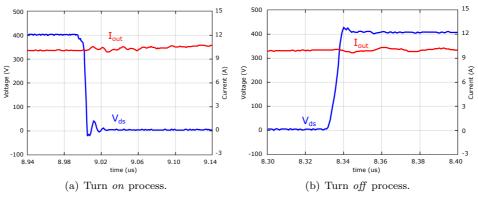

|      | Turn on and off processes of cascode $GaN$ HEMT transistor                                  | 75 |

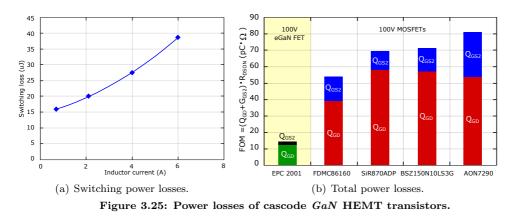

| 3.25 | Power losses of cascode <i>GaN</i> HEMT transistors.                                        | 76 |

| 4.1          | Current ideal balance in discrete parallel devices and parallel mod-                                                             |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|

|              | ules                                                                                                                             |

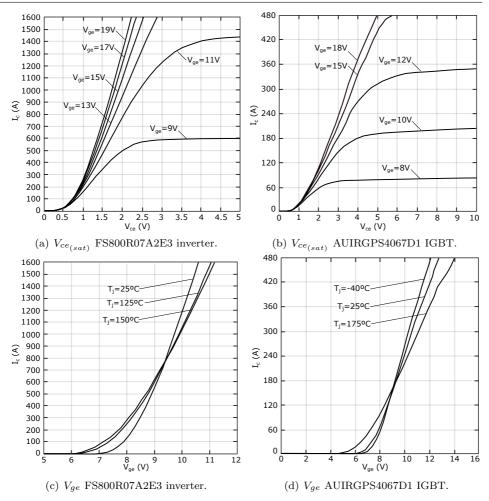

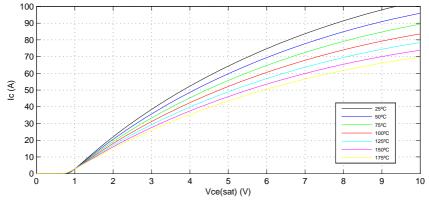

| 4.2          | Characteristic curves of de $I_c$ vs $V_{ce_{(sat)}}$ and $I_c$ vs $V_{ge}$                                                      |

| 4.3          | Saturation voltage positive coefficient with $V_{ge} = 18 V. \dots 84$                                                           |

| 4.4          | Evolution of de $V_{ce_{(sat)}}$ according to $T_j$ and $I_c$                                                                    |

| 4.5          | $\Delta I_c$ between two IGBTs according their characteristic curve and $T_j$ . 86                                               |

| 4.6          | Main parameters of the dynamic behaviour                                                                                         |

| 4.7          | Transit variation according to temperature                                                                                       |

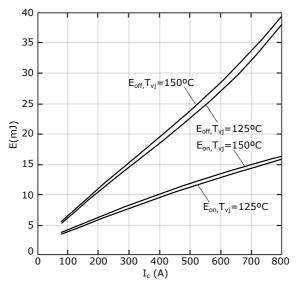

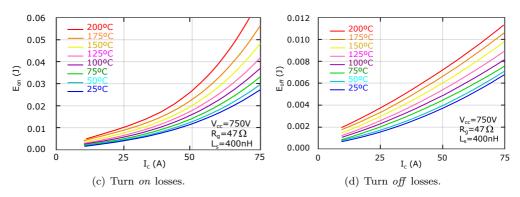

| 4.8          | Switching losses according to $T_j$                                                                                              |

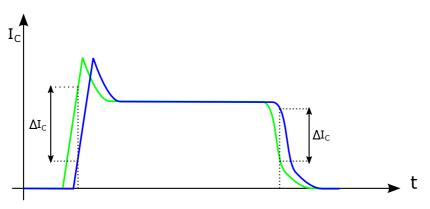

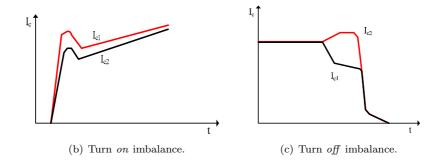

| 4.9          | Dynamic current imbalance during turn on and off 90                                                                              |

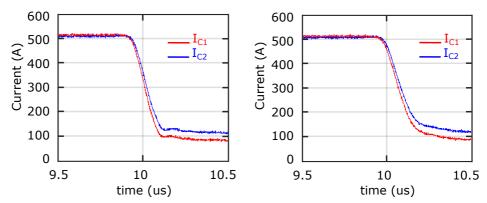

| 4.10         | Turn off process and power loss variations at different junction                                                                 |

|              | temperature. $\dots \dots \dots$ |

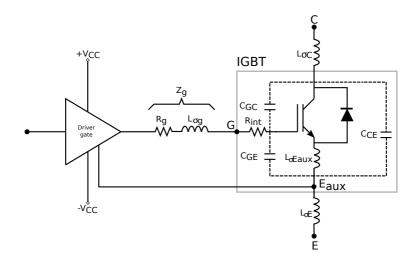

| 4.11         | Driver gate circuit: stray elements distribution                                                                                 |

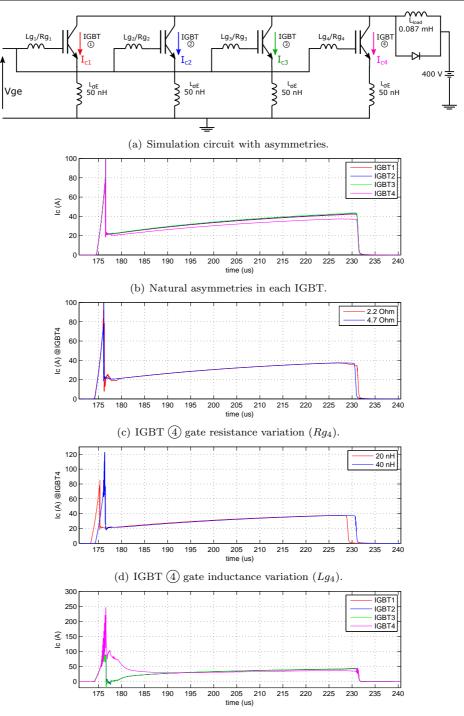

|              | Asymmetries effects produce by gate connection on the current $93$                                                               |

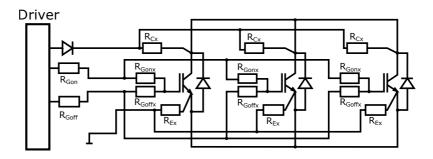

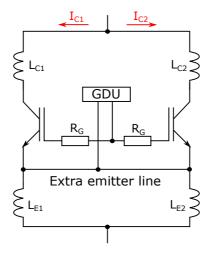

|              | Recommended $driver$ circuit for the IGBT parallelization 95                                                                     |

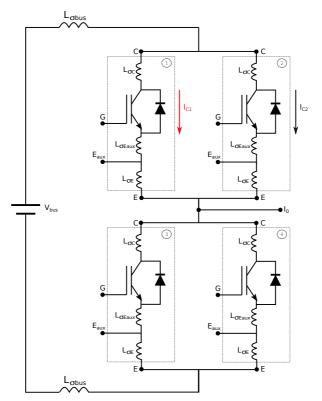

| 4.14         | Branch of parallelized IGBT with parasitic elements and imbalance                                                                |

|              | effects                                                                                                                          |

|              | Equivalent circuit with parallel connections and its main inductances. $99$                                                      |

| 4.16         | Feedback examples between power circuit and driver                                                                               |

| 5.1          | Main ports that constitute a have dis based namer module 106                                                                     |

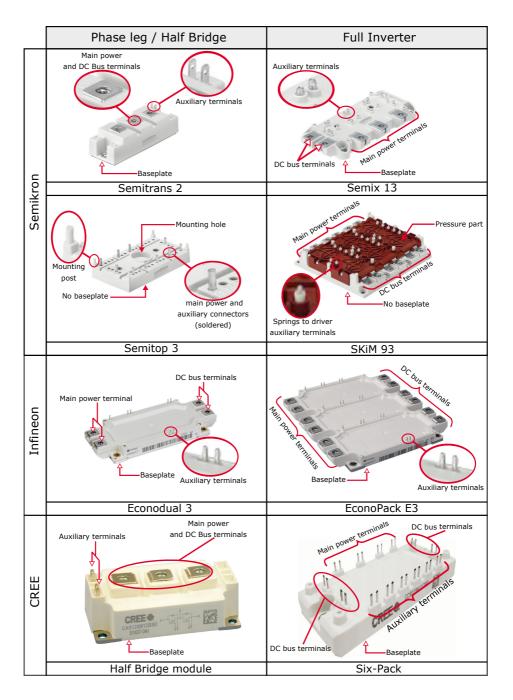

| $5.1 \\ 5.2$ | Main parts that constitute a bare die based power module 106<br>Examples of standard power module encapsulations 107             |

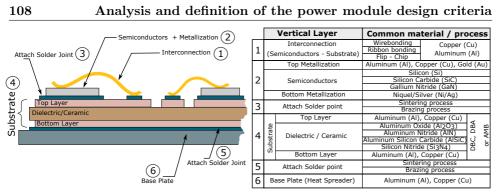

| 5.2<br>5.3   | General substrate structure for a power application                                                                              |

| 5.3<br>5.4   | Gate current loop and feedback effects                                                                                           |

| $5.4 \\ 5.5$ | Different gate attack options in commercial half-bridge power mod-                                                               |

| 0.0          | ules                                                                                                                             |

| 5.6          | Power loop device interconnection and stray inductance variation. 117                                                            |

| 5.7          | Examples of applying symmetry over a DBC design                                                                                  |

| 5.8          | Examples of control and power terminals over a power module 122                                                                  |

| 5.9          | General design process for power modules based on standard so-                                                                   |

|              | lutions                                                                                                                          |

|              |                                                                                                                                  |

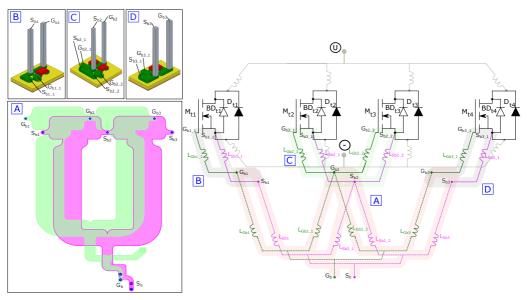

| 6.1          | Circuits and analysis applied in each power circuit                                                                              |

| 6.2          | Layout designs of a parallelized switch with their equivalent circuit<br>132                                                     |

| 6.3          | Substrate configuration of power switch alternatives $(ADS^{TM})$ 133                                                            |

| 6.4          | $Z_{ge}$ and $Z_{ce}$ measures for each design at 10 kHz                                                                         |

| 6.5          | $V_{ge}$ signals for the designs of a power switch with 4 IGBT parallelized.136 $$                                               |

| 6.6          | IGBT currents and $I_{ce},R_{ce}$ and $L_{ce}$ variations with frequency. $~$ 138                                                |

| 6.7          | 3D current density distribution at 10 kHz                                                                                        |

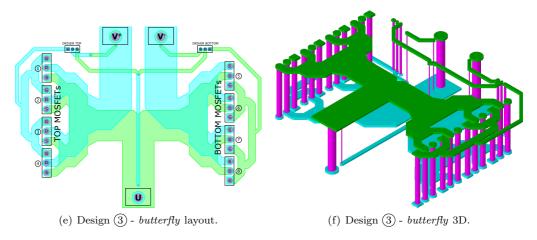

| 6.8          | Half-bridge PCB with 4 SiC MOSFET in parallel                                                                                    |

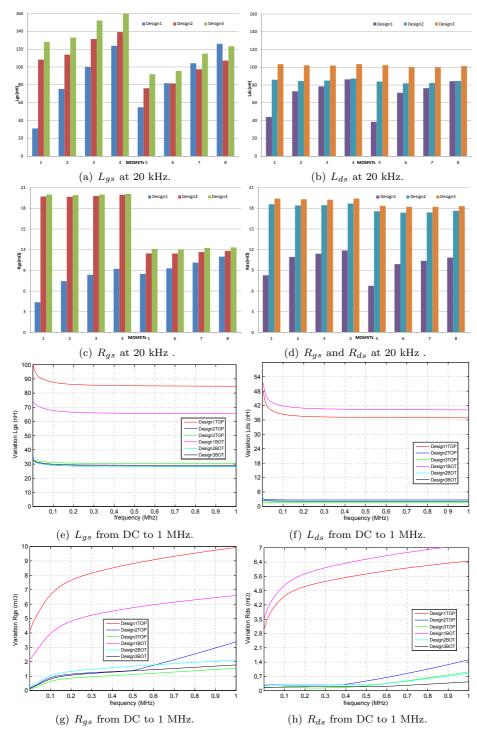

| 6.9          | Equivalent parasitic impedance variations                                                                                        |

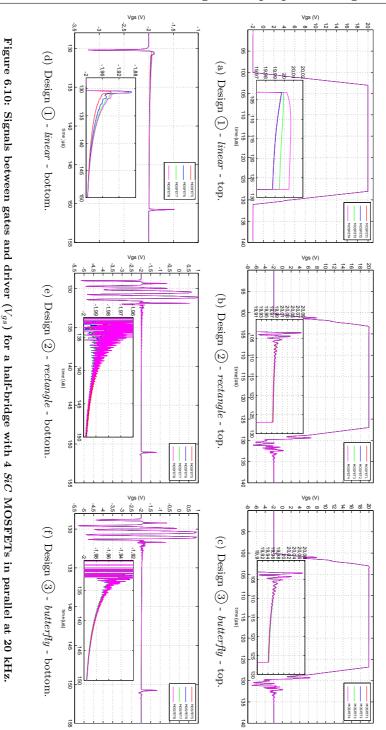

| 6.10  | Signals between gates and driver $(V_{gs})$ for a half-bridge with 4 SiC                                           | 140 |

|-------|--------------------------------------------------------------------------------------------------------------------|-----|

| 0.11  | MOSFETs in parallel at 20 kHz.                                                                                     | 146 |

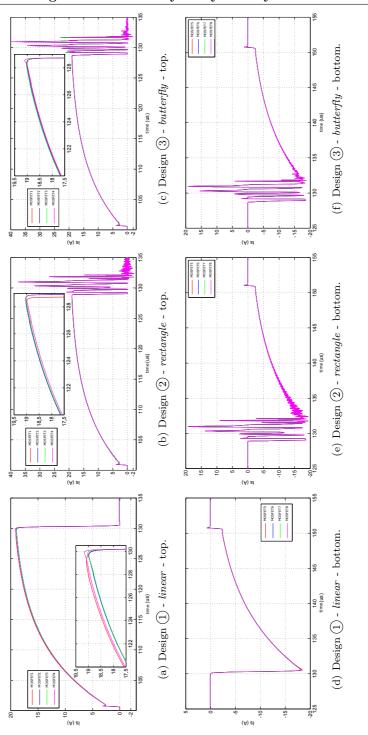

| 6.11  | Current over the $SiC$ MOSFETs top and bottom for each design                                                      |     |

|       | at 20 kHz.                                                                                                         | 147 |

| 6.12  | 2 Current density distribution in top and bottom layers for each                                                   |     |

|       | design at 20 kHz.                                                                                                  | 149 |

| 6.13  | Enhanced butterfly design implementing round tracks and cutting                                                    |     |

|       | edges                                                                                                              |     |

| 6.14  | Enhanced half-bridge design explaining layout improvements                                                         | 152 |

| 6.15  | Enhanced <i>butterfly</i> half-bridge design closed loop impedances, gate                                          |     |

|       | signals and current $SiC$ MOSFETS                                                                                  | 153 |

| 6.16  | 5 DC bus main structures and its multilayer substrate                                                              | 155 |

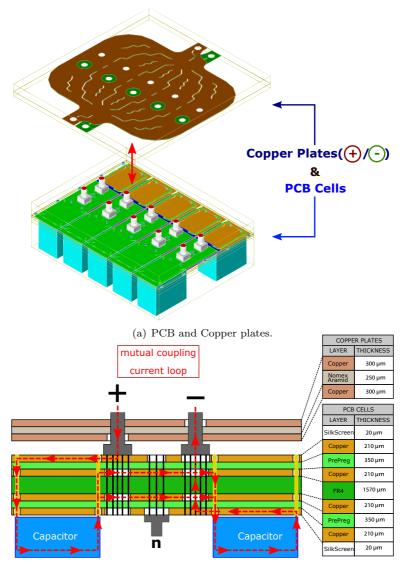

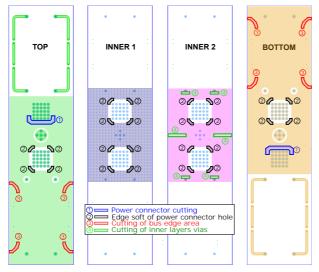

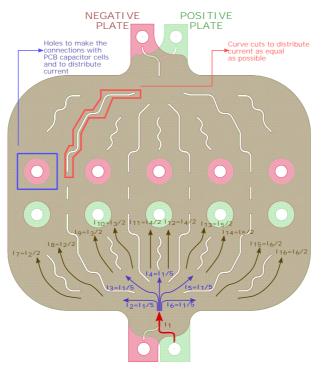

| 6.17  | Power multilayer PCB and copper plates.                                                                            | 156 |

| 6.18  | Capacitor cell simulations and experimental data                                                                   | 158 |

| 6.19  | Copper plates simulations and experimental data                                                                    | 160 |

|       | ) Impedance values of PCB cells + copper plates                                                                    |     |

|       | Current measures in copper plate and PCB cell                                                                      |     |

|       | Current density distribution at different frequencies in the layers                                                |     |

| -     | of PCB cell capacitors and in the positive copper plate                                                            | 163 |

|       |                                                                                                                    |     |

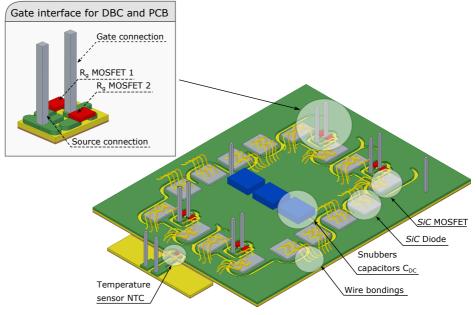

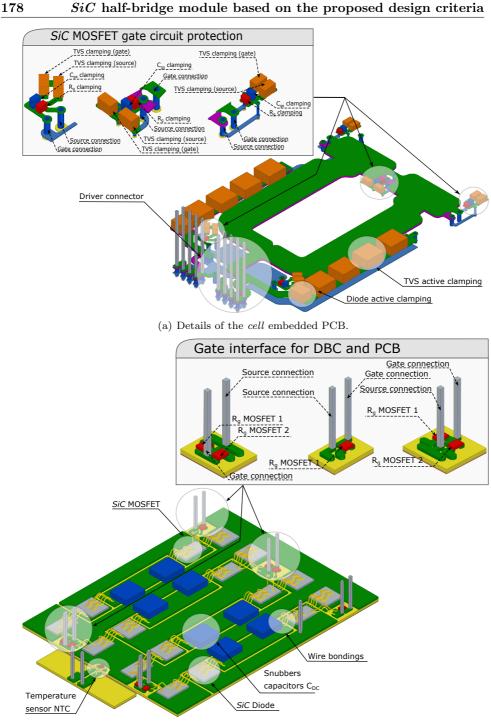

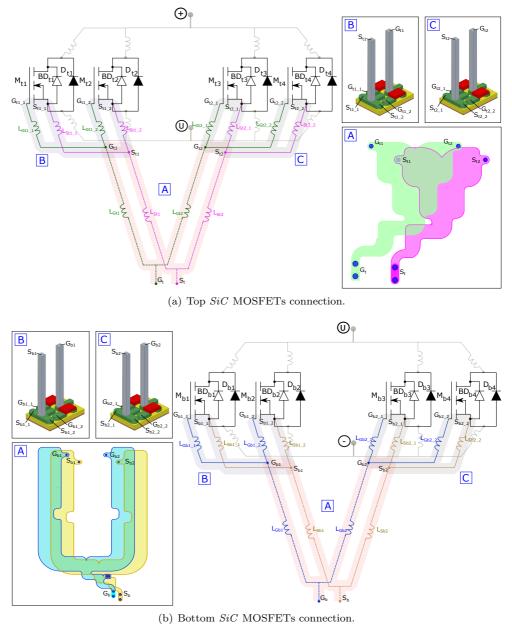

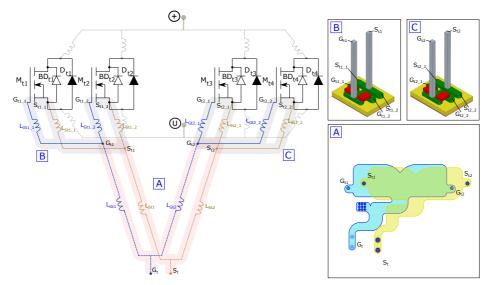

| 7.1   | Proposed $SiC$ half-bridge power module designs                                                                    | 167 |

| 7.2   | P-Cell and N-Cell configuration.                                                                                   | 168 |

| 7.3   | Symmetric power module design: embedded PCB and DBC                                                                |     |

|       | schematics.                                                                                                        | 169 |

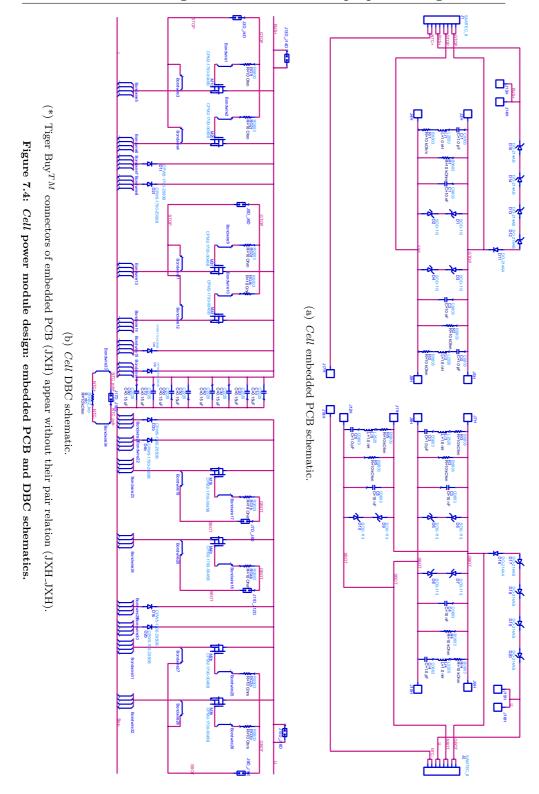

| 7.4   | Cell power module design: embedded PCB and DBC schematics.                                                         |     |

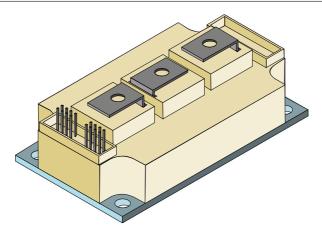

| 7.5   | Power module mechanics based on SEMITRANS solution                                                                 |     |

| 7.6   | Power module $ADS^{TM}$ simulation stack-up                                                                        |     |

| 7.7   | Details of PCB and DBC for the <i>symmetric</i> power module design.                                               |     |

| 7.8   | Details of PCB and DBC in the <i>cell</i> power module design                                                      |     |

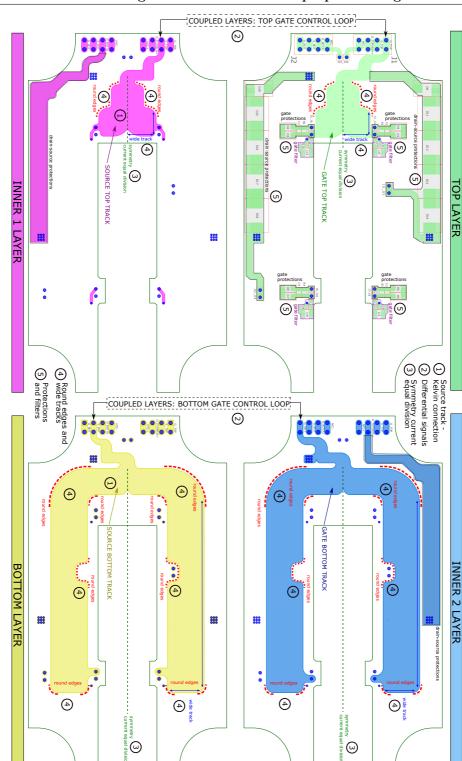

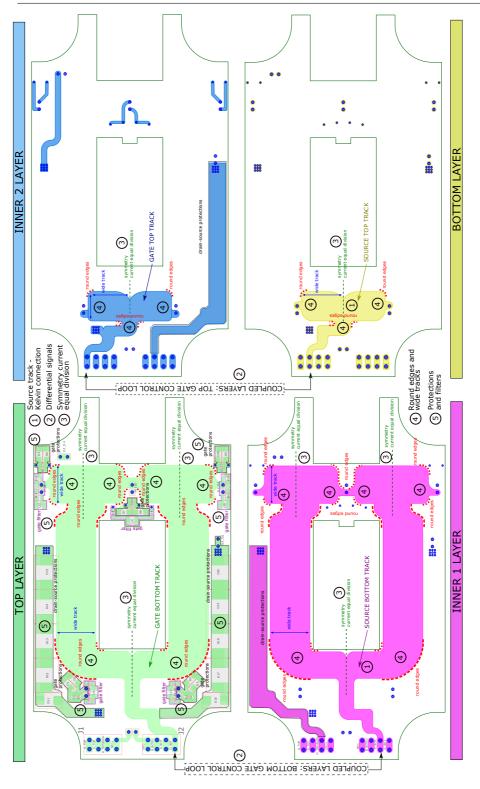

| 7.9   | Gate attack PCB layer of the symmetric design.                                                                     |     |

|       | Gate attack PCB layer of the <i>cell</i> design                                                                    |     |

|       | Gate attack i CD layer of the <i>extr</i> design.                                                                  |     |

|       | 2 Gate attack circuit of the <i>cell</i> design                                                                    |     |

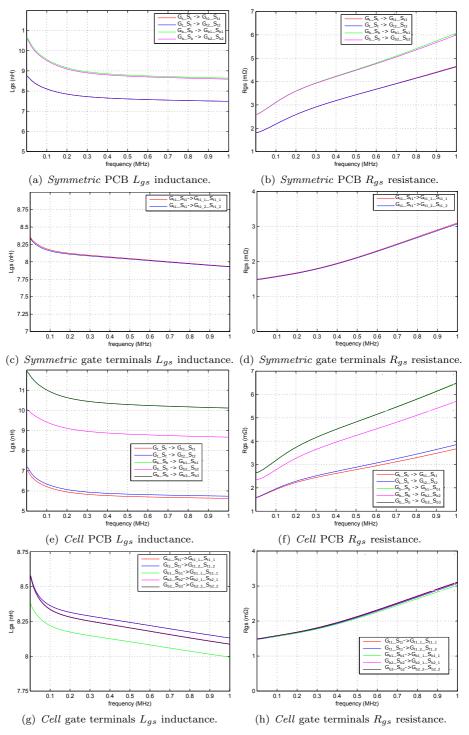

|       | Gate attack impedances for <i>symmetric</i> and cell <i>designs</i>                                                |     |

|       | Gate attack impedances for symmetric and cen usigns Gate attack voltage and current signals for symmetric and cell | 100 |

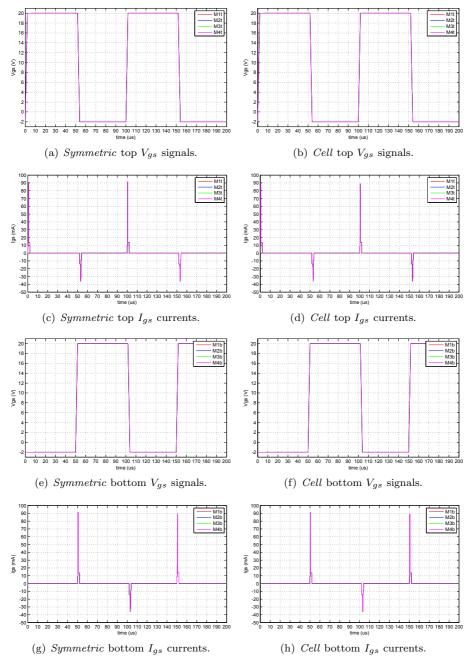

| 1.14  | designs                                                                                                            | 106 |

| 7 1 5 | 0                                                                                                                  |     |

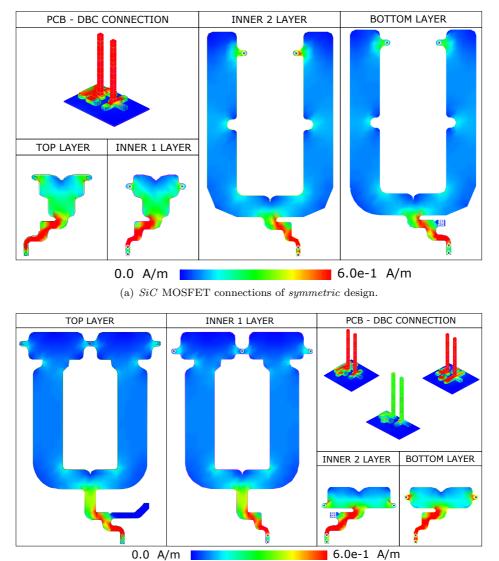

|       | Gate attack current density distribution. $\dots \dots \dots \dots \dots$                                          |     |

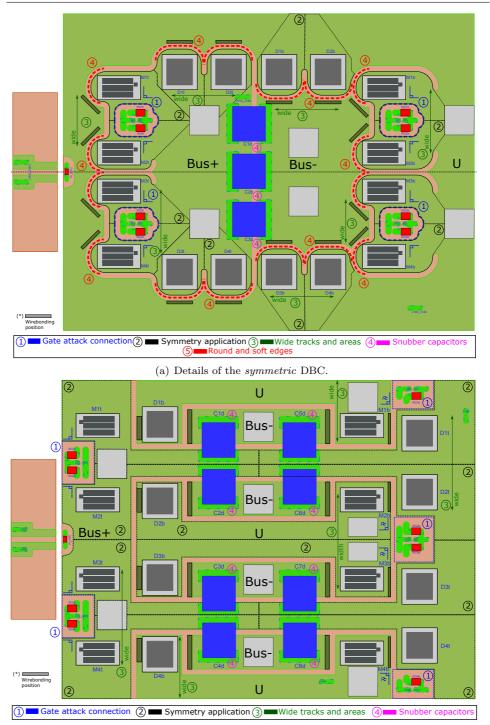

|       | Details of each power layout proposal (symmetric and cell DBCs).                                                   |     |

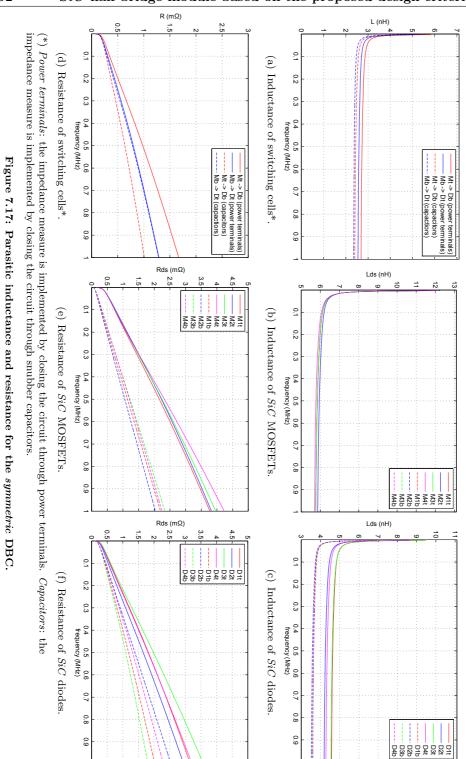

|       | Parasitic inductance and resistance for the <i>symmetric</i> DBC                                                   |     |

|       | Parasitic inductance and resistance for the <i>cell</i> DBC                                                        |     |

| 7.19  | Device switching loop currents for the <i>symmetric</i> and <i>cell</i> designs.                                   | 194 |

|     | ٠ | ٠ |

|-----|---|---|

| XXV | 1 | 1 |

|     | - | - |

| 7.20 | Power layout current density distribution for the <i>symmetric</i> and  |

|------|-------------------------------------------------------------------------|

| - 04 | cell proposals                                                          |

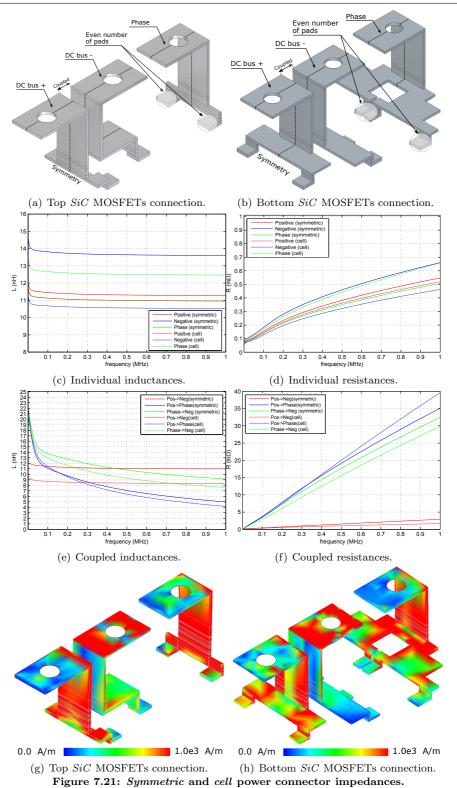

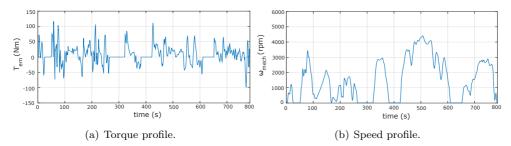

|      | Symmetric and cell power connector impedances                           |

| 7.22 | Torque and speed Fleet-BEV driving cycle profiles applied during        |

|      | the simulations                                                         |

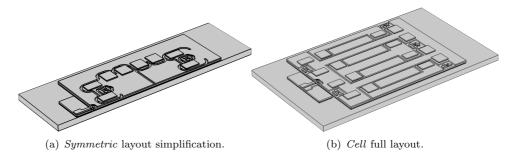

| 7.23 | Half-bridge power layouts used in COMSOL Multiphysics simula-           |

|      | tions                                                                   |

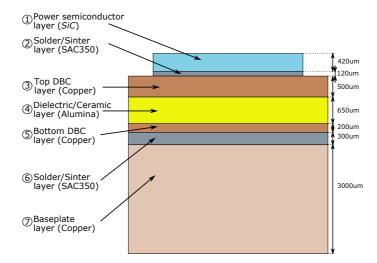

| 7.24 | Power substrate for thermal simulations in COMSOL Multiphysics. 201     |

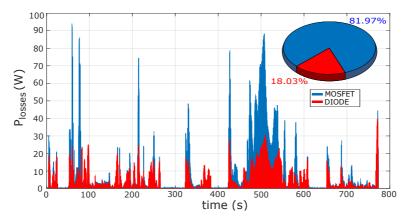

| 7.25 | Initial power losses distribution between $SiC$ MOSFETs and diodes. 202 |

| 7.26 | Thermal responses and equivalent Foster networks for symmetric          |

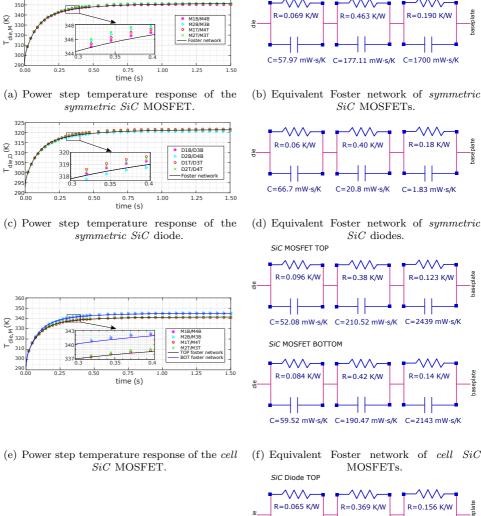

|      | and <i>cell</i> half-bridge power layout                                |

| 7.27 | Power dissipation profiles of power semiconductors for <i>symmetric</i> |

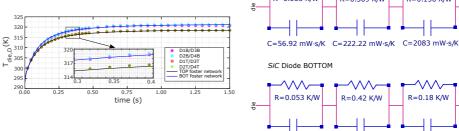

|      | and <i>cell</i> layouts: heat sources of the electro-thermal model 204  |

| 7.28 | 3D temperature distributions (°C) obtained on the symmetric and         |

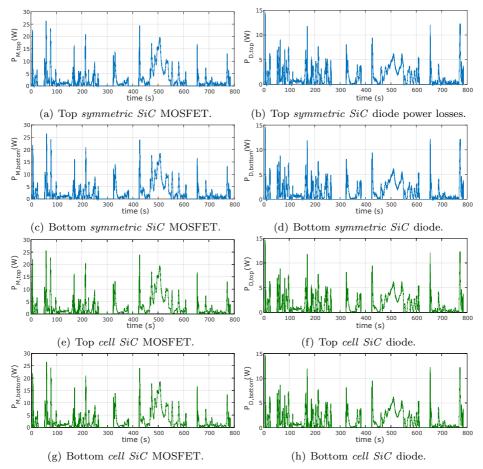

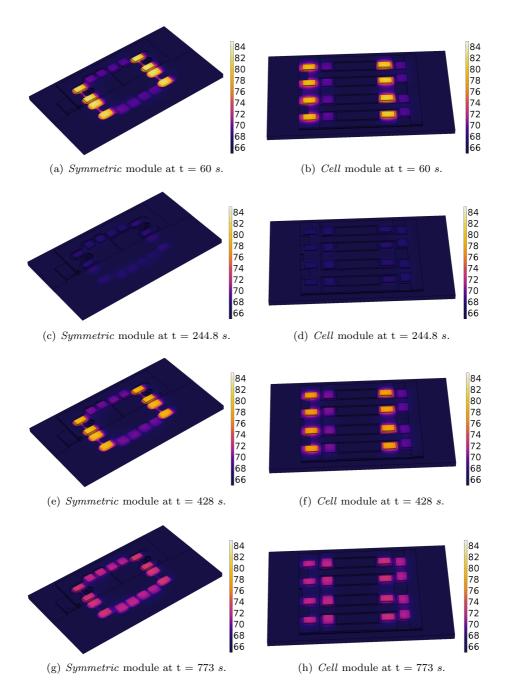

| 0    | <i>cell</i> power modules                                               |

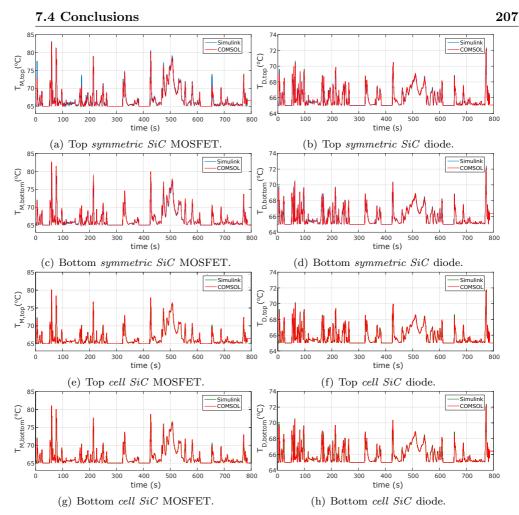

| 729  | Junction temperature profiles of power semiconductors during the        |

| 1.20 | complete driving cycle for both symmetric and cell power modules. 207   |

|      | complete univing cycle for both symmetric and cent power modules. 201   |

| A.1  | Parasitic elements of paths in power layouts                            |

| A.2  | Extraction of parasitic elements of a circuit                           |

| A.3  |                                                                         |

| 11.0 | Arina cluster                                                           |

|      | <i>Arma</i> clustel                                                     |

| B.1  | General diagram of the proposed methodology to characterize the         |

| D.1  | electro-thermal behaviour of an automotive power module through         |

|      | driving cycles                                                          |

| B.2  | General diagrams of the 1D RT and 3D FEM simulations 238                |

|      | 0                                                                       |

| B.3  | Flowchart of the procedure applied to extract the Foster networks. 240  |

## List of Tables

| 1.1                                              | Electric mobility performance class overview for passenger vehicles<br>and commercial vehicles/buses                              |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1.2                                              | Summary of the most relevant multiphase architectures suitable for HEV/EV drive systems, including their corresponding references |

| 1.3                                              | and main features                                                                                                                 |

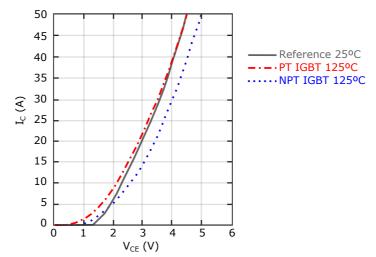

| $2.1 \\ 2.2$                                     | PT and NPT technology comparative                                                                                                 |

| 3.1                                              | SiC semiconductor technologies, listing their most relevant advantages and disadvantages                                          |

| 5.1                                              | SiC/Si electric automotive inverters for HEV/EV drive systems 104                                                                 |

| $\begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \end{array}$ | Substrate materials used in the half-bridge designs                                                                               |

| 7.1<br>7.2<br>7.3                                | Symmetric power module design components                                                                                          |

| 7.4                                              | Main properties of the DBC substrate for thermal simulation 201                                                                   |

| 8.1                                              | Publications extracted form this PhD thesis and document chapters.221                                                             |

| B.1                                              | Qualitative comparison between 3D FEM, 1D Cauer/Foster and the proposed hybrid simulation procedures                              |

# List of Acronyms

| 1D                     | 1 Dimension                            |

|------------------------|----------------------------------------|

| 2DEG                   | 2-D electron gas                       |

| 3D<br>3D               | 3 Dimensions                           |

| 3D<br>AC               |                                        |

| AMB                    | Alternating current                    |

|                        | Active metal brazing                   |

| BJT                    | Bipolar junction transistor            |

| CHB                    | Cascade H-bridge                       |

| CTE                    | Coefficient of thermal expansion       |

| CSTBT                  | Carrier stored gate bipolar transistor |

| DBA                    | Direct bonded aluminium                |

| DBC                    | Direct bonded copper                   |

| $\mathrm{DC}$          | Direct current                         |

| $\mathrm{DfR}$         | Design for reliability                 |

| DLC                    | Direct lead bonding                    |

| DOE                    | United States Department of Energy     |

| DSP                    | Digital signal processor               |

| D-mode                 | Depletion mode                         |

| $\mathbf{E}\mathbf{M}$ | Electromagnetic method                 |

| EMC                    | Electromagnetic compatibility          |

| $\mathbf{EMF}$         | Electromotive force                    |

| EMI                    | Electromagnetic Interference           |

| E-mode                 | Enhancement mode                       |

| EV                     | Electric vehicle                       |

| $\mathbf{FC}$          | Flying capacitor                       |

| FCell                  | Fuel cell vehicle                      |

| FEM                    | Finite element method                  |

|                        |                                        |

| $\mathbf{FS}$  | Field stop                                                 |

|----------------|------------------------------------------------------------|

| FWD            | Freewheeling diode                                         |

| FZ             | Float zone                                                 |

| GHG            | Greenhouse gas                                             |

| GRG            | Generalized reduced gradient method                        |

| HEMT           | High electron mobility transistor                          |

| $\mathrm{HEV}$ | Hybrid electric vehicle                                    |

| HPC            | High performance computing                                 |

| HSEM           | High speed electric machine                                |

| HV             | High voltage                                               |

| HVDC           | High voltage direct current                                |

| ICE            | Internal combustion engine                                 |

| IEA            | International Energy Agency                                |

| IGBT           | Insulated gate bipolar transistor                          |

| $_{\rm JBS}$   | Junction barrier schottky                                  |

| JFET           | Junction field effect transistor                           |

| $LC_{JFET}$    | Lateral channel junction field effect transistor           |

| LPT            | Light punch through                                        |

| MIS-HEMT       | Metal insulator semiconductor gate field effect transistor |

| MOSFET         | Metal oxide semiconductor field effect transistor          |

| MPS            | Merged PN schottky diode                                   |

| MTBF           | Mean time between failures                                 |

| NEDC           | New European driving cycle                                 |

| NPC            | Neutral point clamped                                      |

| NPT            | Non punch through                                          |

| p-HEMT         | p-GaN gate Field effect transistor                         |

| OEM            | Original equipment manufacturer                            |

| PCB            | Printed circuit board                                      |

| PCC            | Power converter circuits                                   |

| PEEC           | Partial element equivalent circuit                         |

| PHEV           | Plug-in hybrid electric vehicle                            |

| PEEC           | Partial element equivalent circuit                         |

| PiN            | p- $n$ diode with intrinsic region                         |

| $\mathbf{PM}$  | Permanent magnet                                           |

| PT             | Punch through                                              |

| PMSM           | Permanent magnet synchronous machine                       |

| RB             | Reverse blocking                                           |

|                |                                                            |

| RC                  | Reverse conducting                                      |

|---------------------|---------------------------------------------------------|

| R&D                 | Research and development                                |

| $\operatorname{RE}$ | Range extended                                          |

| RT                  | Real time                                               |

| SAE                 | Society of Automotive Engineers                         |

| SBD                 | Schottky barrier diode                                  |

| SJT                 | Super junction transistor                               |

| SPT                 | Soft punch through                                      |

| TIM                 | Thermal interface material                              |

| Trench FS           | Trench field stop                                       |

| UN ESCAP            | United Nations Economic and Social Commission for Asia  |

| USCAR               | United States Council for Automotive Research           |

| $VT_{JFET}$         | Vertical trench junction field effect transistor        |

| WBG                 | Wide bandgap                                            |

| WLTP                | Worldwide harmonized light-duty vehicles test procedure |

# List of Symbols

| α              | Thermal expansion coefficient $(K^{-1})$                      |

|----------------|---------------------------------------------------------------|

| $\lambda$      | Thermal conductivity $(W/(m \cdot K))$                        |

| Â              | Area of a surface $(m^2)$                                     |

| $BD_{xy}$      | Body diode top or bottom $(x)$ and number of branch $(y)$ (-) |

| $C_{DC}$       | DC-link capacitor $(F)$                                       |

| $C_{th}$       | Thermal capacitance $(W \cdot s/K)$                           |

| d              | Thickness of a layer (m)                                      |

| $D_{xy}$       | Diode top or bottom $(x)$ and number of branch $(y)$ (-)      |

| $D_b$          | Drain bottom connection (-)                                   |

| $D_t$          | Drain top connection (-)                                      |

| freq           | Frequency (Hz)                                                |

| $G_b$          | Gate bottom connection (-)                                    |

| $G_t$          | Gate top connection (-)                                       |

| $I_{max}$      | Maximum semiconductor current (A)                             |

| $I_{rr}$       | Recovery current (A)                                          |

| $L_o$          | Overall length of the material (m)                            |

| $L_b$          | Equivalent parasitic inductance of bonding (H)                |

| $L_{bd}$       | Drain bottom equivalent inductance (H)                        |

| $L_{bs}$       | Source bottom equivalent inductance (H)                       |

| $L_d$          | Drain equivalent parasitic inductance (H)                     |

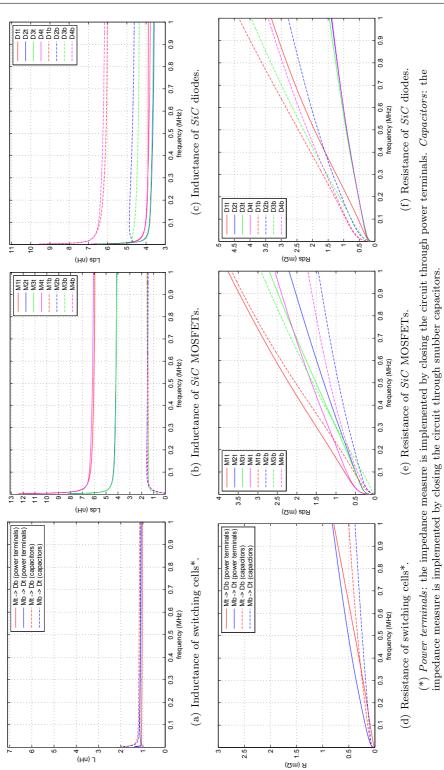

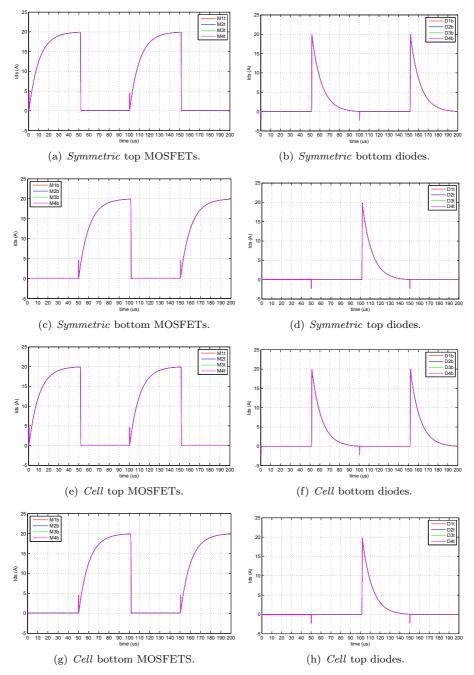

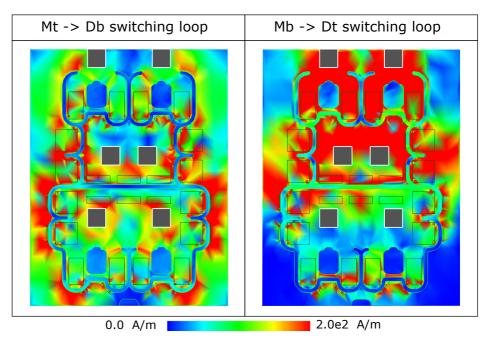

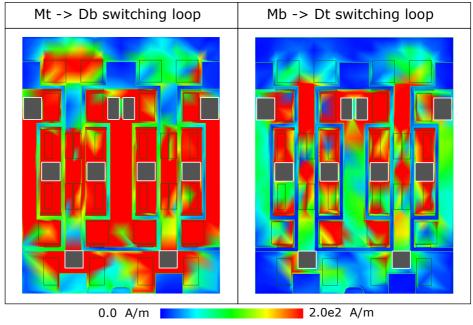

| $L_{dBUS}$     | Drain DC-link equivalent inductance (H)                       |